FPGA implementation method of fiber channel 64-bit parallel scrambling and descrambling

An implementation method, 64-bit technology, applied in instruments, computers, calculations, etc., can solve the problems of difficult FPGA implementation and high speed, and achieve high-speed results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

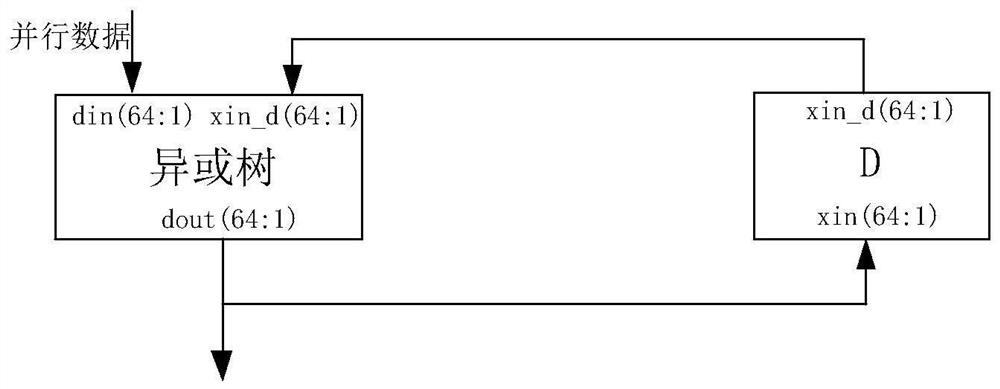

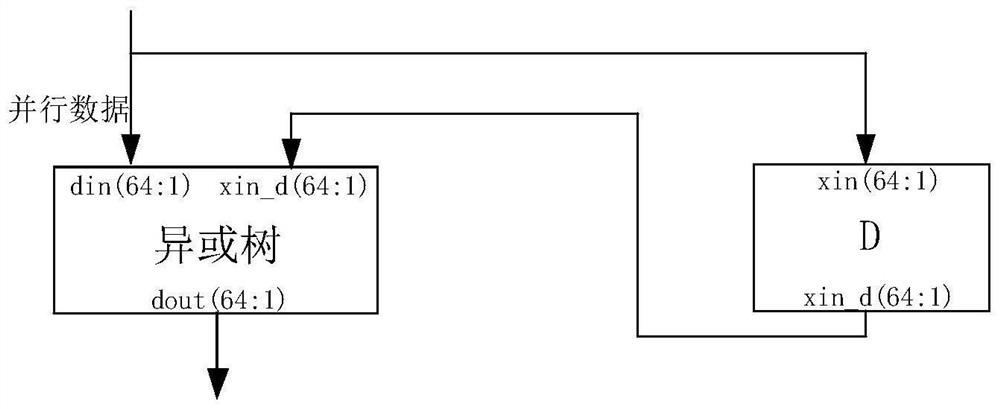

[0024] The FPGA implementation method of the Fiber channel 64-bit parallel scrambling and descrambling device described in the present invention includes a scrambling implementation method and a descrambling implementation method.

[0025] The scrambling implementation method is as follows figure 1 Shown, is to use an XOR tree and a delay unit ( figure 1 In D) realize 64 parallel scramblings, the output of the XOR tree is the output after scrambling; the input data of the delay unit is the output data of the XOR tree, and the output data of the XOR tree is delayed After time processing, it is used as the output data of the delay unit.

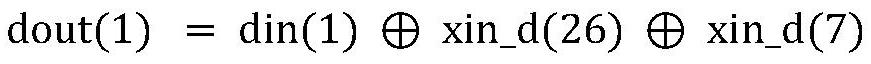

[0026] The input data of the XOR tree is the 64-bit parallel data that needs to be scrambled and the 64-bit data output by the delay unit. The 64-bit data obtained after the input data is calculated is used as the output data of the XOR tree. The calculation formula is:

[0027] Formula 1: Bits 1-39 of the output data are:

[0028] Formu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com