FPGA-based dynamic partial reconfiguration system and method

A technology for dynamic partial reconfiguration and storage of subsystems, applied to the architecture with a single central processing unit, CAD circuit design, digital computer components, etc., can solve the problem of reducing the secondary development characteristics of reconfiguration technology, low real-time Reduce structural efficiency and other issues, achieve the effect of shortening the time of data interaction, shortening the development cycle, and improving the configuration speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

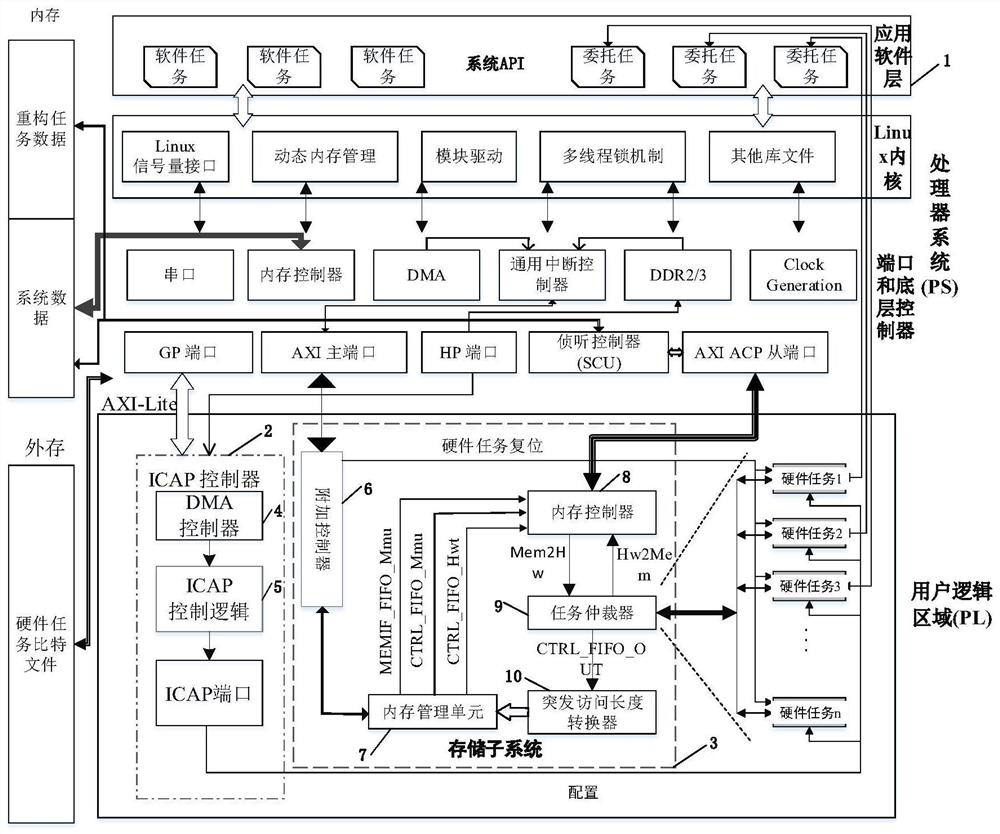

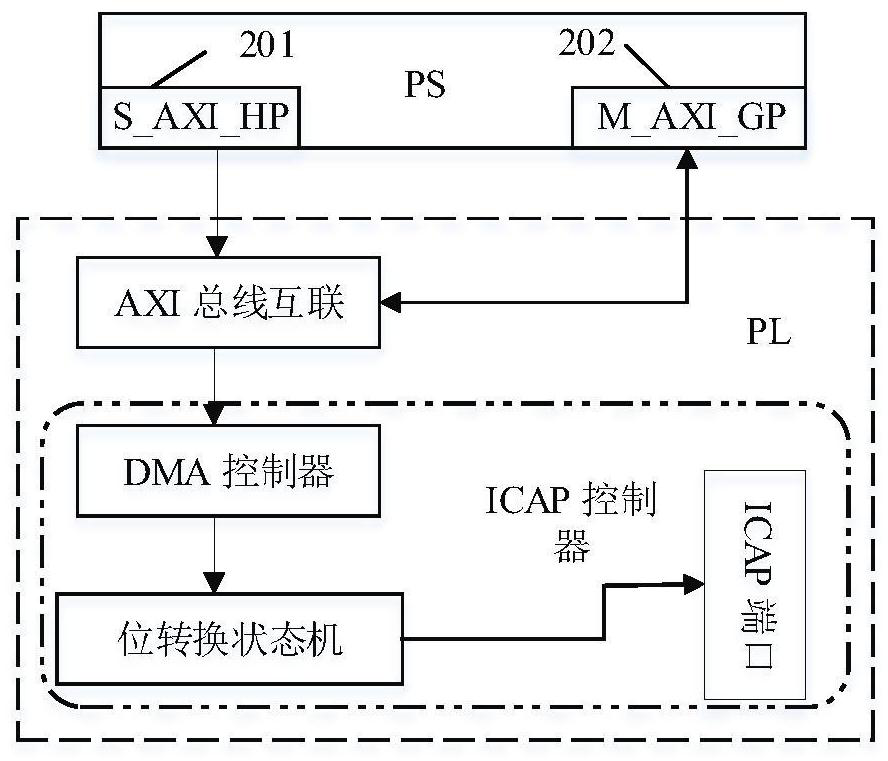

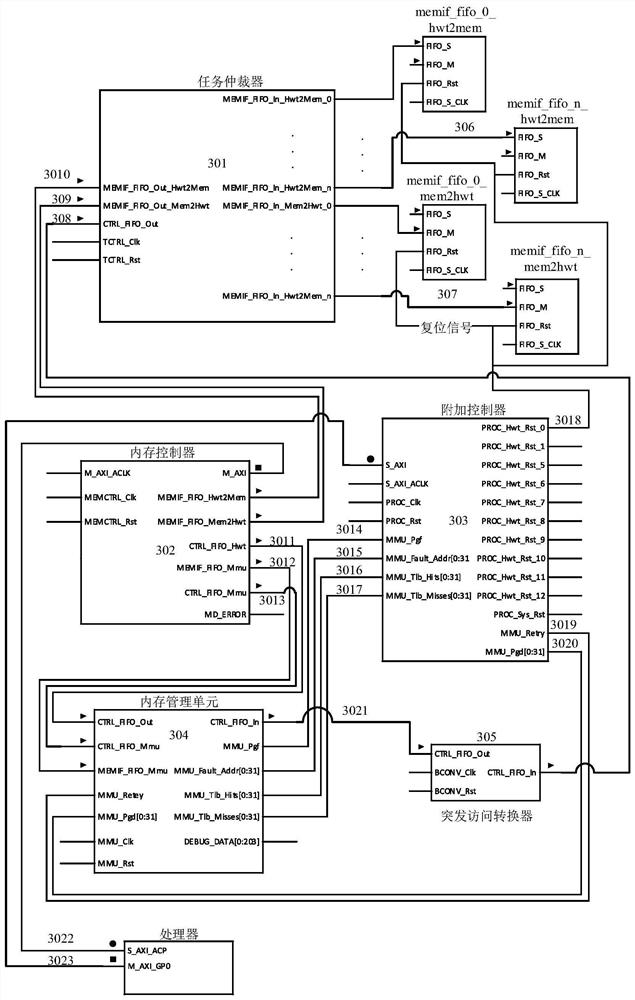

[0031] The present invention provides an FPGA-based dynamic partial reconfiguration system, the purpose of which is to provide users with a programming model composed of hardware tasks, software tasks and entrusted tasks, and realize dynamic loading of hardware tasks through dynamic reconfiguration technology, design And realized the storage subsystem used for data interaction between hardware task and system application software layer. The system reduces the difficulty of reconfiguration application development, reduces the user's direct operation on the underlying hardware of the device, and accelerates the development speed of reconfiguration applications.

[0032] The invention provides a dynamic partial reconfiguration system based on FPGA, and its technical scheme is: on the basis of the multi-thread programming model of the embedded Linux system, combined with the partial dynamic reconfiguration characteristics of FPGA, a system based on hardware tasks and software tasks...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com