An efficient clock tree physical location optimization method for integrated circuit semi-custom backend design

A technology of physical location and integrated circuits, applied in electrical digital data processing, computer-aided design, calculation, etc., can solve the problem of no unified and efficient clock tree design physical placement optimization method, shorten the chip design cycle and improve design quality , reduce the effect of ineffective work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention discloses a method for optimizing the physical location of an efficient clock tree in integrated circuit semi-customized back-end design. The specific implementation of the present invention will be further described below in combination with preferred embodiments.

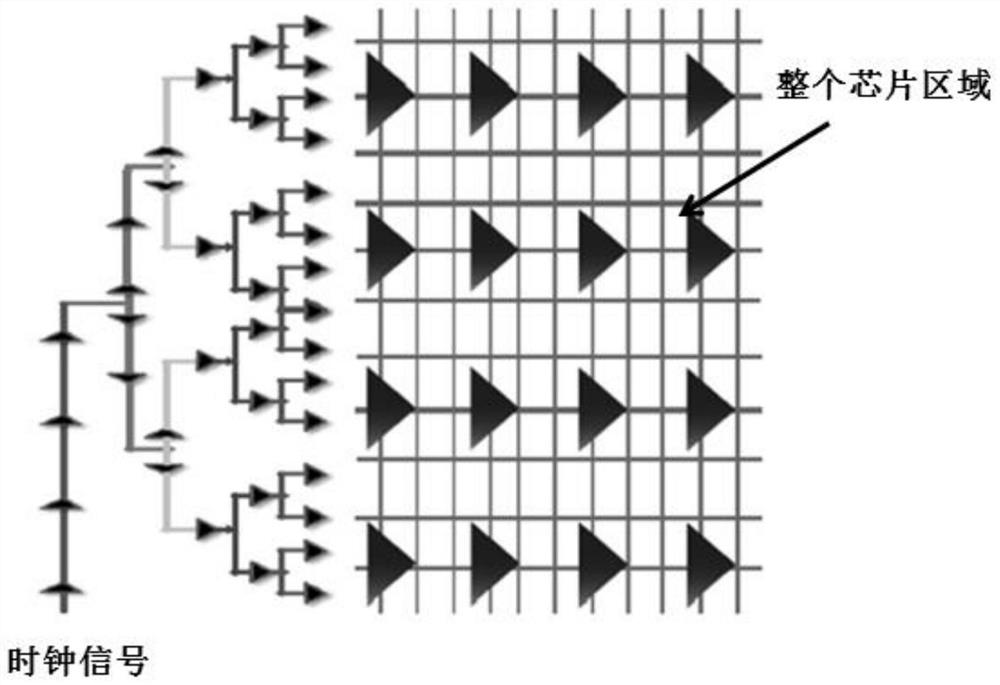

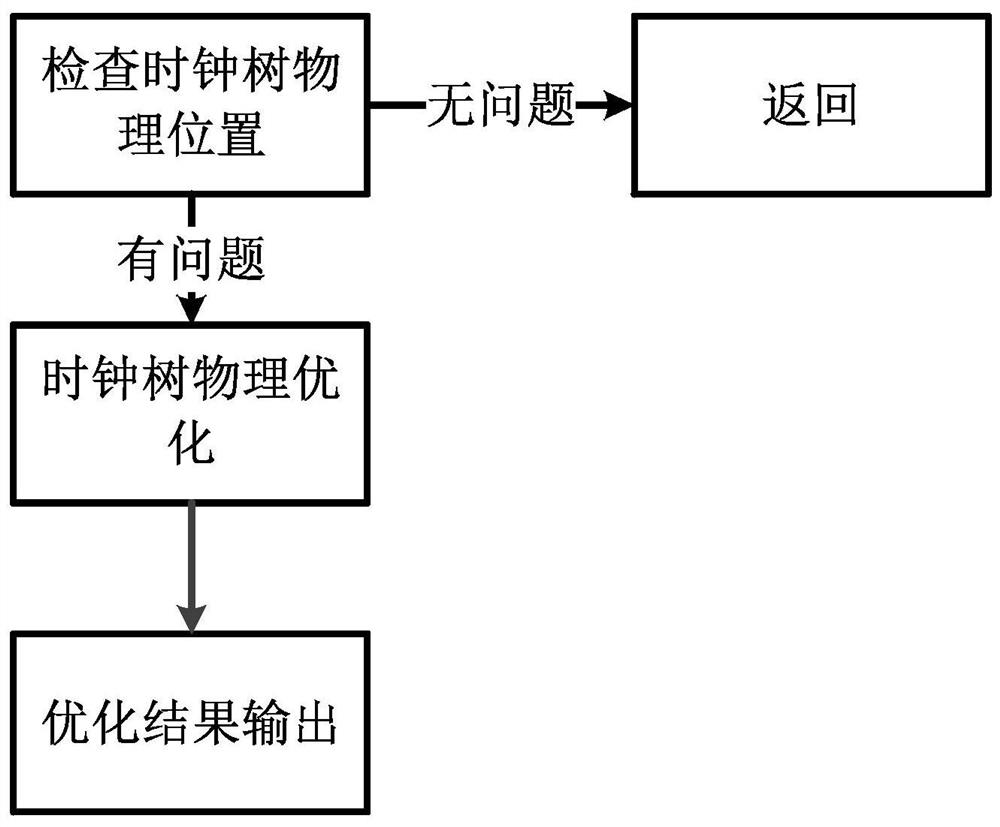

[0028] see attached Figure 1 to Figure 6 , image 3 The specific flow of the method for optimizing the physical location of the high-efficiency clock tree in integrated circuit semi-custom back-end design is shown.

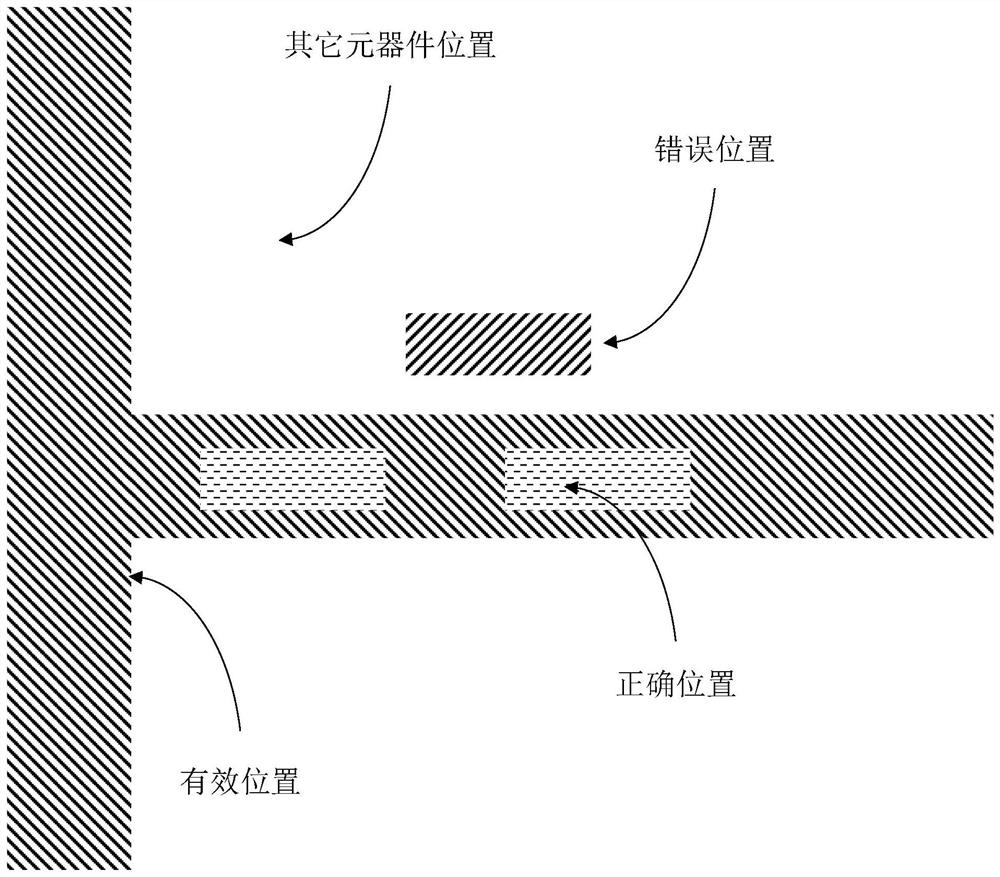

[0029] see attached image 3 and Figure 4 and Figure 5 , the integrated circuit semi-customized back-end design efficient clock tree physical location optimization method includes the following steps:

[0030] Step S1: The back-end design tool checks one by one according to the chip shape and the electrical parameters of the components and judges whether each physical position of the clock tree is reasonable. If it is reasonable, check the next physical position of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com