Pulsed laser single particle testing device and testing method for bare chip

A pulsed laser and test device technology, applied in the direction of measuring devices, electronic circuit testing, non-contact circuit testing, etc., can solve the problems of increasing the uncertainty of test results, fewer components, and the inability to quantitatively evaluate the incident laser energy loss, etc., to achieve Save development costs, avoid damage, and ensure smooth progress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

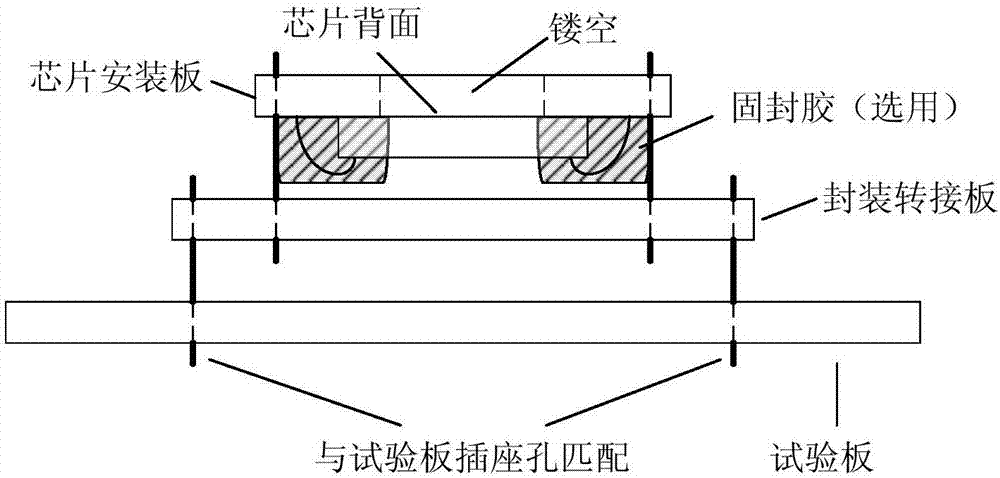

[0067] Such as figure 1 As shown, a pulsed laser single particle test device for a bare chip, the device includes a chip mounting board, a packaging adapter and a test board;

[0068] The chip mounting board is used to fix the PROM chip to be tested. The metal wiring area of the chip is 0.4mm×1.5mm, and the chip is diced into a size of 0.8mm×2mm. The area should be larger than the metal wiring area of the chip to be tested, and the chip scribing size should be larger than the hollow area. The back of the chip to be tested is fixed on the lower surface of the chip mounting board with glue around the back, and the back of the chip to be tested is bonded to the lower surface of the chip mounting board; the chip to be tested is facing down, and the hollow through holes are arranged according to the arrangement of the solder joints of the chip to be tested Corresponding pads and corresponding pins are used as lead-out pins. Bonding wires are used to make sequential electrical ...

Embodiment 2

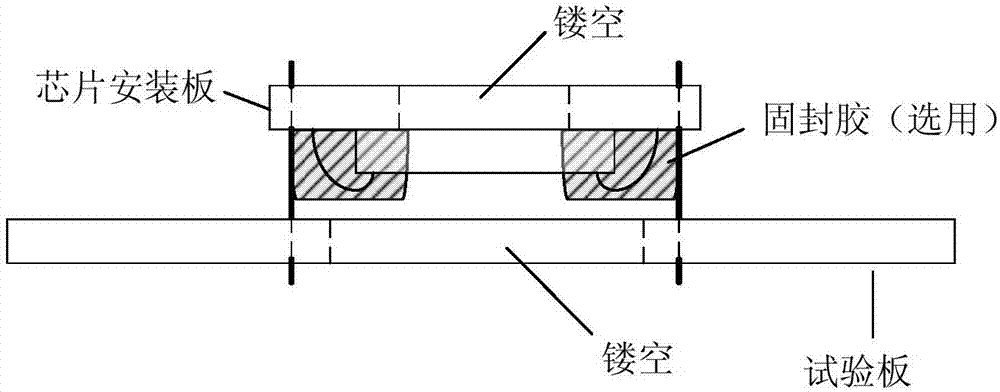

[0071] Such as figure 2 As shown, a pulsed laser single particle test device for a bare chip, the device includes a chip mounting board and a test board;

[0072] The chip mounting plate is used to fix the CMOS image sensor chip to be tested. The metal wiring area of the chip is 1.5mm×4.5mm, and the chip is diced to a size of 2.1mm×5.1mm. The hollow area in the center of the chip mounting plate is designed to be 1.8mm ×4.8mm, the hollowed out area should be larger than the metal wiring area of the chip to be tested, and the chip scribing size should be larger than the hollowed out area. The back of the chip to be tested is fixed and installed on the lower surface of the chip mounting plate with glue, and the back of the chip to be tested is attached to the lower surface of the chip mounting plate; pad, and there are pins electrically connected to the pad as lead-out pins, the solder joints of the chip to be tested and the pad are electrically connected sequentially with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com