Layout wiring scheme tMesh of multi/many-core framework TriBA-CMPs

A technology of layout and routing and routing methods, which is applied in the field of layout and routing solutions of multi-core architecture TriBA-CMPs, can solve problems such as unfavorable process implementation, and achieve the effect of simple and easy layout and routing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0093] In tMesh's wiring-related claims, there are options of first horizontal and then vertical or first vertical and then horizontal, Figure 5 Both options are characterized with a 3-core (i.e., 1-layer) tMesh layout. In this figure, when the upper left and lower right coreTiles of TriBA-cNoC are interconnected, they can be wired horizontally and then vertically or vertically and then horizontally; the coreTile and L 2 When interconnecting, wiring can be done horizontally and then vertically or vertically and then horizontally.

Embodiment 2

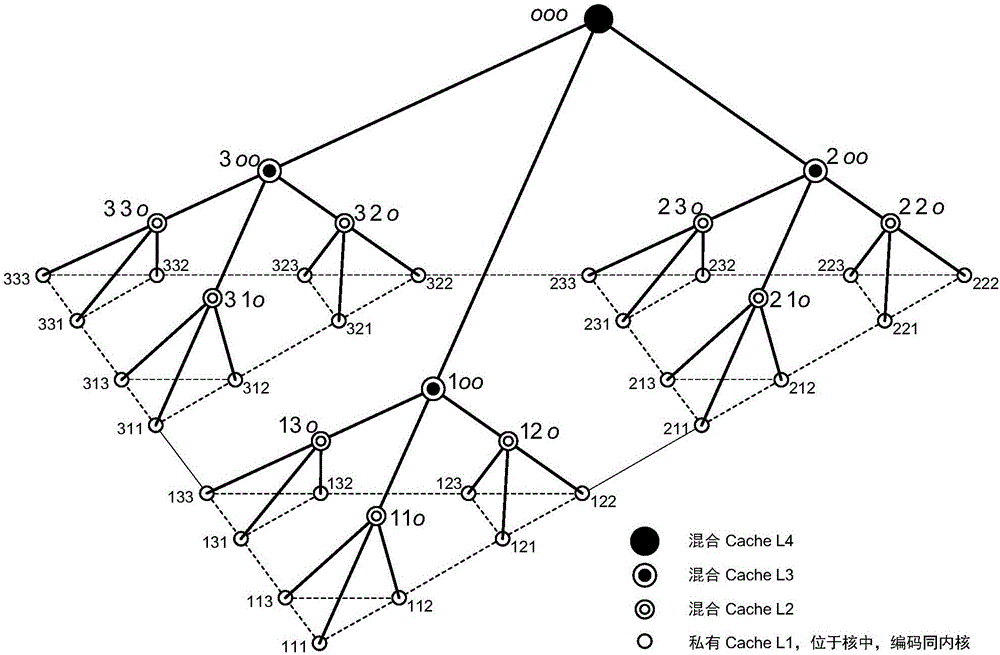

[0095] Because TriBA-mNoC may have multiple input and output ports in the actual implementation, so its horizontal (vertical) connection may exist Image 6 Multiple connections are shown. In TriBA-mNoC wiring of layer f tMesh, upper left and lower right L in layer f-1 tMesh f Level Cache units are respectively connected with L in layer f tMesh f+1 When level Cache is connected, L f Level Cache unit has 2 f-2 cacheTile and L f+1 Level Cache is horizontally and vertically adjacent respectively, so they can be accessed through 2 f-2 The horizontal and vertical wiring are connected, and can also be connected through 2 f-2 Any one or more of the horizontal and vertical wirings are connected to each other; L in the lower left f-1 layer tMesh f Level Cache unit and L in layer f tMesh f+1 Level Cache connected, through the L f cacheTile and L in the upper right corner of the level Cache unit f+1 The cacheTile in the lower right corner of the level Cache unit is connected to r...

Embodiment 3

[0097] Such as Figure 7 As shown, tMesh can be applied after horizontal or vertical reflection and rotation at any angle to meet different application requirements.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com