Digital low-dropout voltage stabilizer

A low-dropout voltage regulator, digital technology, applied in the direction of instruments, electrical variable adjustment, control/regulation systems, etc., can solve the problems of complex loop compensation, large chip area, low cost, etc., and achieve small output voltage ripple, The effect of small chip area and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

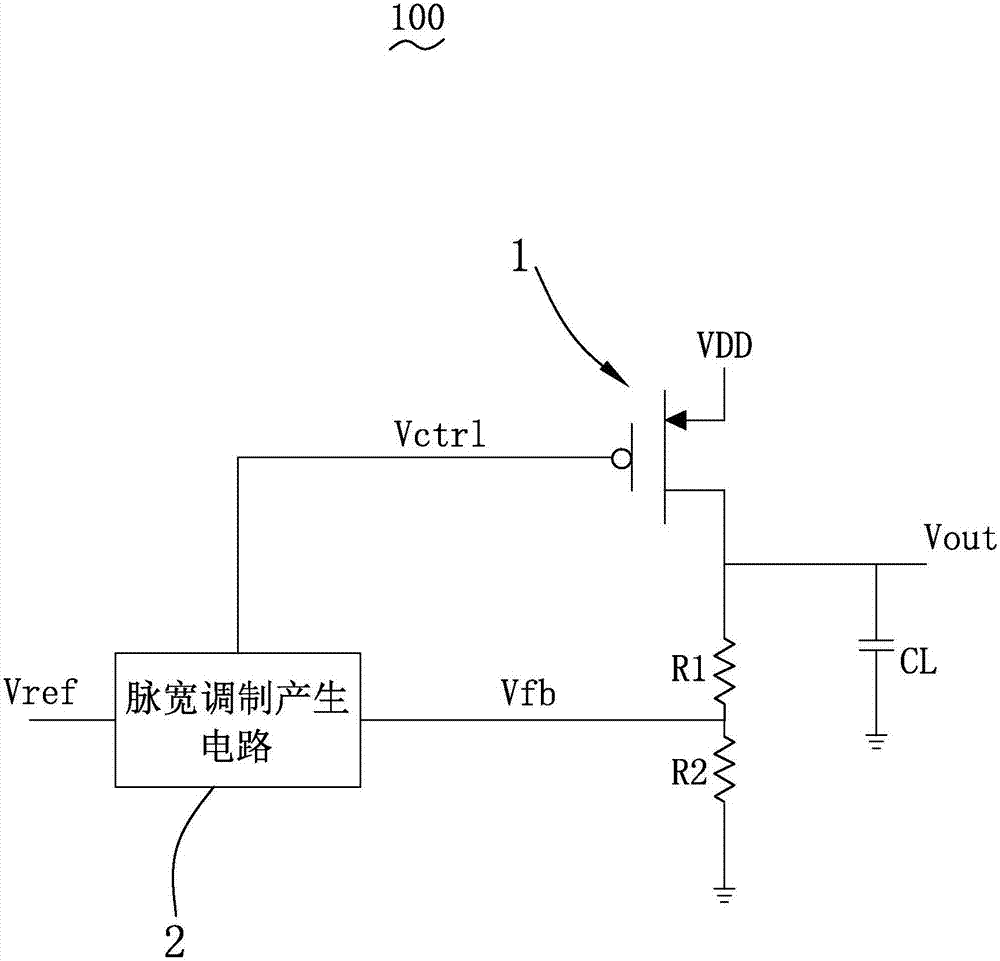

[0029] see figure 1 , is a structural block diagram of the digital low dropout regulator of the present invention. The present invention provides a digital low dropout voltage regulator 10, including a power adjustment transistor 1, a first sampling resistor R1, a second sampling resistor R2, a pulse width modulation generating circuit 2, and a load and compensation capacitor CL.

[0030] The power adjustment transistor is a PMOS transistor or an NMOS transistor, or a PNP transistor or an NPN transistor. In this embodiment, the power adjustment transistor is a PMOS transistor as an example. The source of the power adjustment transistor 1 is connected to a power supply The voltage VDD is used as the input terminal of the digital low dropout voltage regulator 10 .

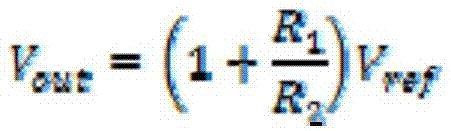

[0031] The drain of the power adjustment transistor 1 is grounded through the first samp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com