Chip package and method for forming the same

A technology for a chip package and a manufacturing method, which is applied to the manufacturing of semiconductor/solid-state devices, semiconductor devices, and electric solid-state devices, etc., can solve the problems of reduced quality and reliability of chip packages, reduced thickness and width of wires, and circuit failures. , to achieve the effect of eliminating electromigration phenomenon, improving quality and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

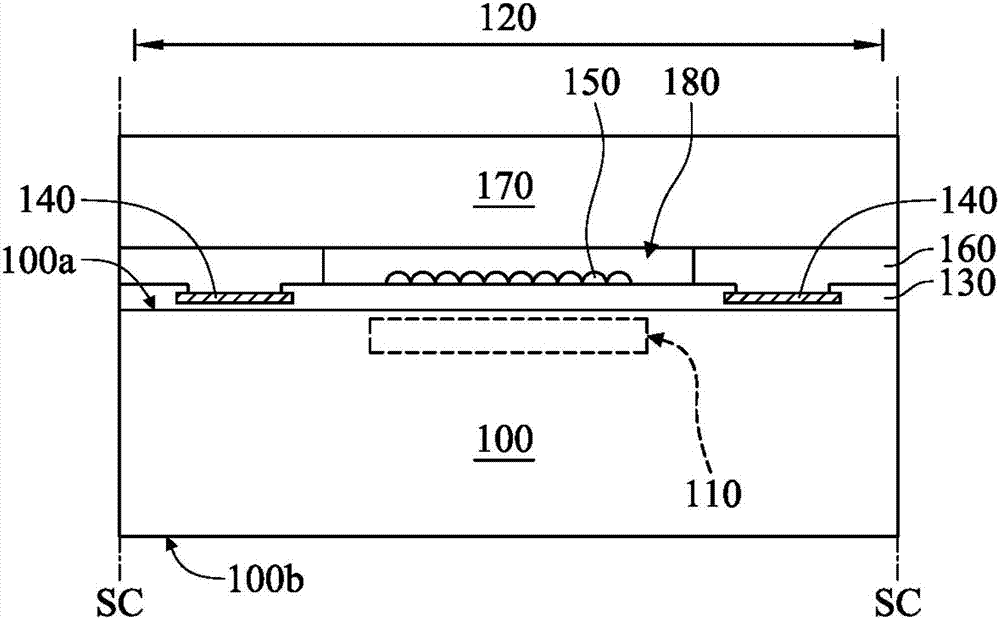

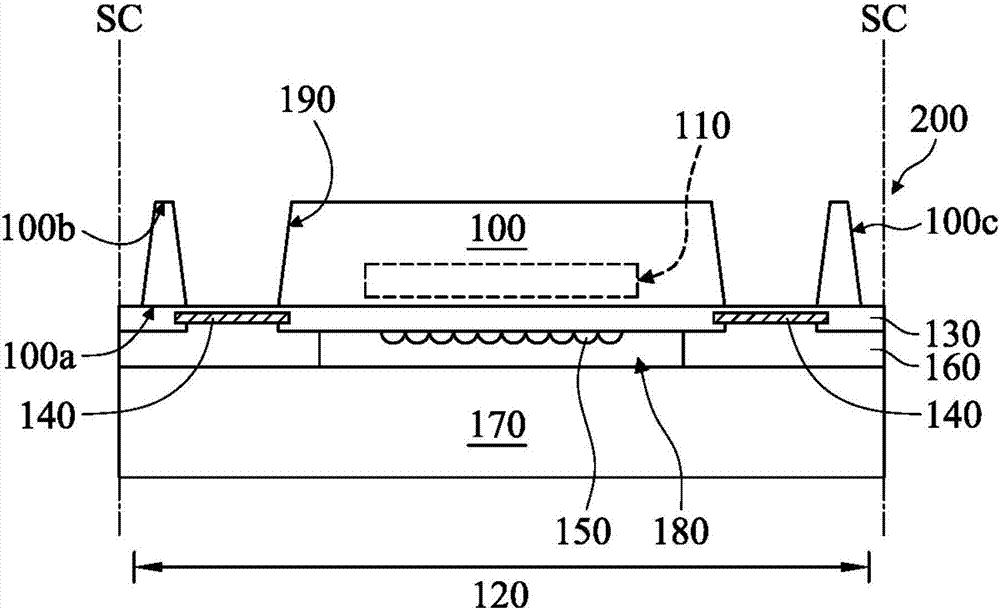

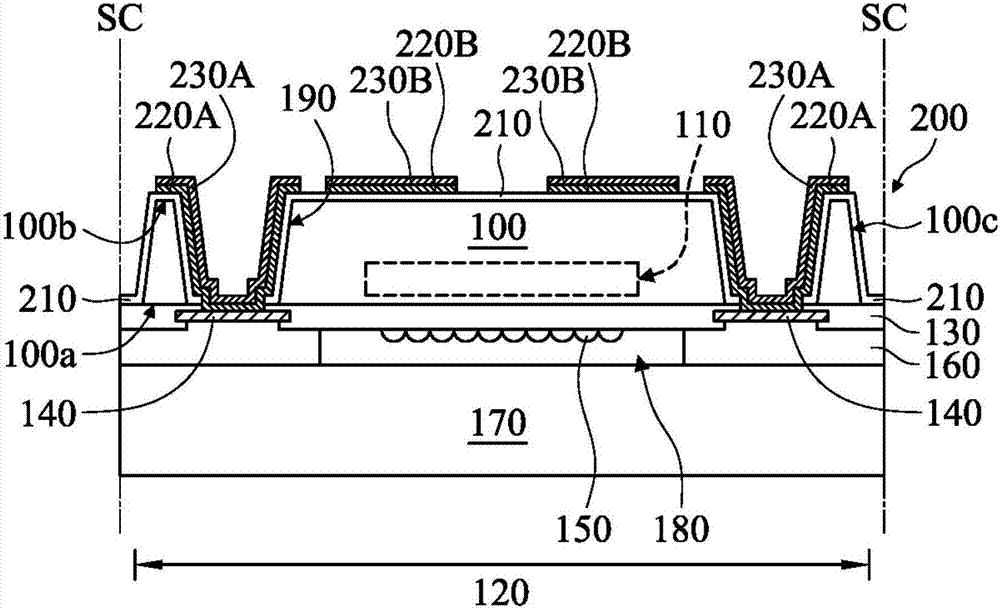

[0014] The fabrication and use of the embodiments of the present invention will be described in detail below. It should be noted, however, that the present invention provides many applicable inventive concepts, which can be embodied in a wide variety of specific forms. The specific embodiments discussed herein are merely specific ways to make and use the invention, and do not limit the scope of the invention. Furthermore, repeated reference numerals or designations may be used in different embodiments. These repetitions are only for the purpose of simply and clearly describing the present invention, and do not represent any relationship between the different embodiments and / or structures discussed. Furthermore, when it is mentioned that a first material layer is located on or above a second material layer, it includes the situation that the first material layer is in direct contact with the second material layer or is separated by one or more other material layers.

[0015] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com