Apparatus and method for producing lateral HEMT

A lateral and buffer layer technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as poor heat dissipation and poor thermal coupling of components, and achieve higher breakdown voltage, reduced leakage current, and improved Effects of off-characteristics and on-characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

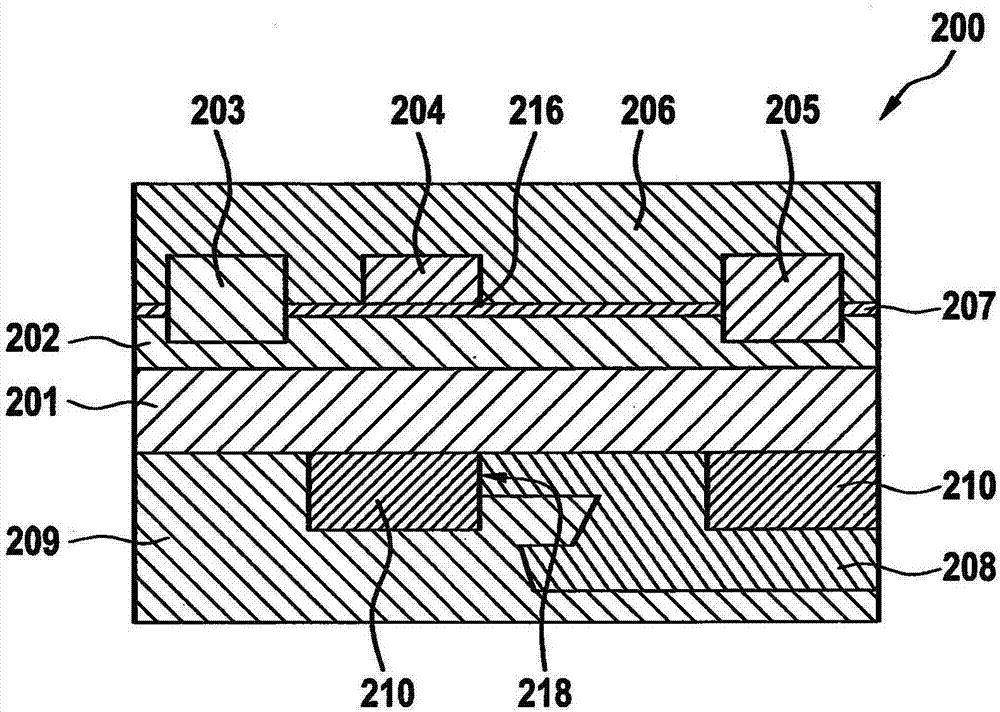

[0036] figure 1 A device 100 with a transverse HEMT according to the invention is shown. In this case, the lateral HEMT has a buffer layer 101 comprising the first semiconductor material. Arranged on the buffer layer 101 is a further semiconductor layer 102 which comprises a second semiconductor material, wherein the second semiconductor material has a different electrode mobility than the first semiconductor material. In other words, a heterostructure is formed because the first semiconductor material and the second semiconductor material are different. A first electrode 103 , a gate 104 and a second electrode 105 are arranged on the further semiconductor layer 102 . Optionally, a gate dielectric layer 107 is disposed on the other semiconductor layer 102 . An insulating protective layer is arranged on the first electrode 103 , the grid 104 and the second electrode 105 , which protects the electrodes 103 , 104 and 105 against mechanical influences. A first field plate 109 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com