Semiconductor testing structure and stress migration testing method

A test structure and stress migration technology, which is applied in semiconductor/solid-state device testing/measurement, semiconductor device, semiconductor/solid-state device manufacturing, etc., can solve the problem of large test time-consuming in the area occupied by the test structure, and improve the utilization of pads efficiency, structure simplification, and area size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

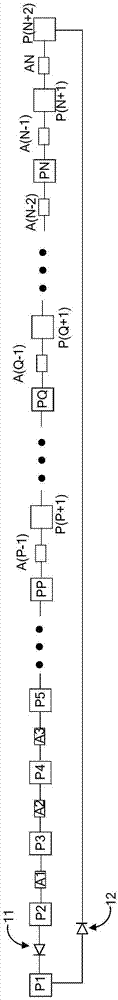

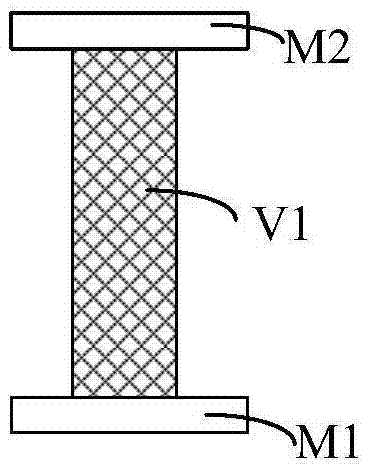

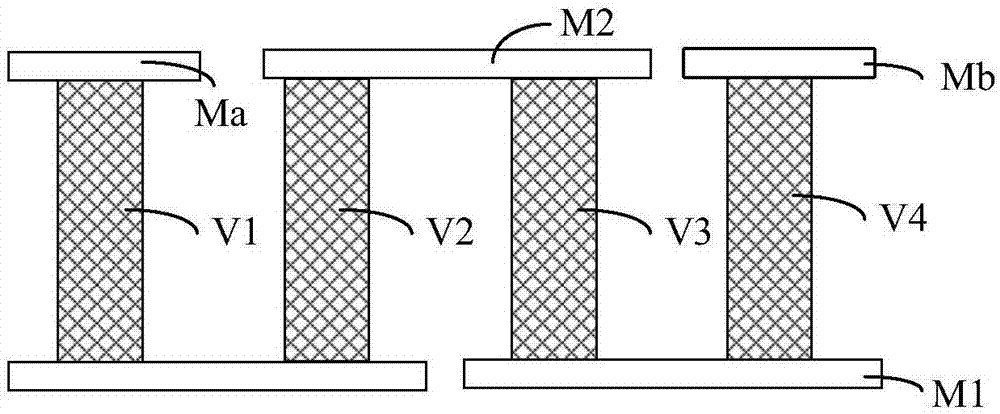

[0033] figure 1 is a schematic diagram of a semiconductor test structure according to an embodiment of the present invention. Figure 2 to Figure 4 yes figure 1 Schematic diagrams of cross-sectional structures of any three sub-test structures from the first sub-test structure, the second sub-test structure, ... to the Nth test structure.

[0034] The following combination Figure 1 to Figure 4 As shown, the semiconductor test structure provided by an embodiment of the present invention is introduced.

[0035] refer to figure 1 As shown, the test structure is formed in the dicing line (not shown) of the wafer, including:

[0036] The first welding pad P1, the second welding pad P2, the third welding pad P3, ..., the N+2th welding pad P...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com