B code time synchronization method based on VPX architecture

A B-code and architecture technology, applied to radio-controlled timers, instruments, digital transmission systems, etc., can solve the problems of low timing accuracy and out-of-synchronization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

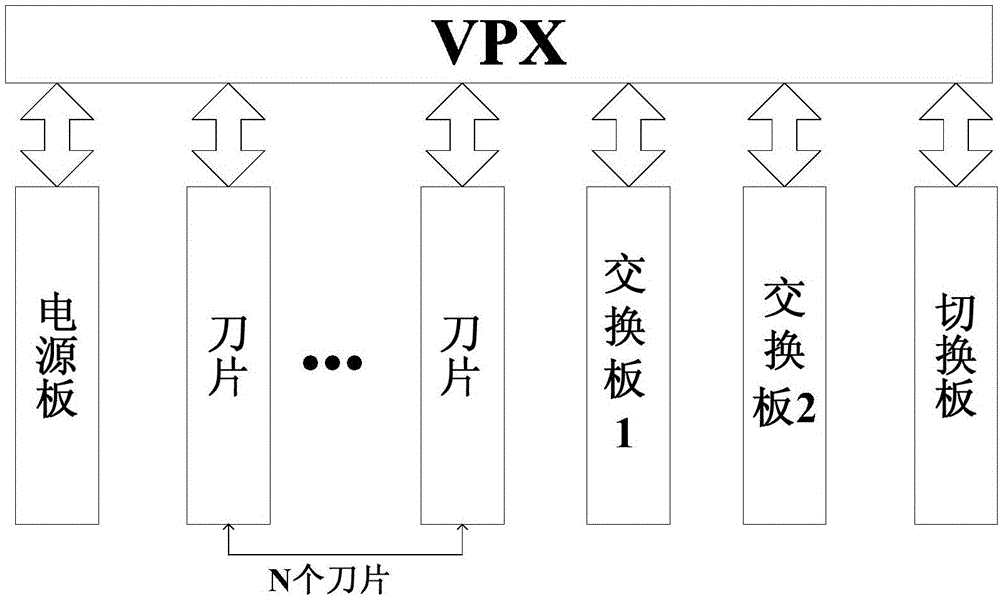

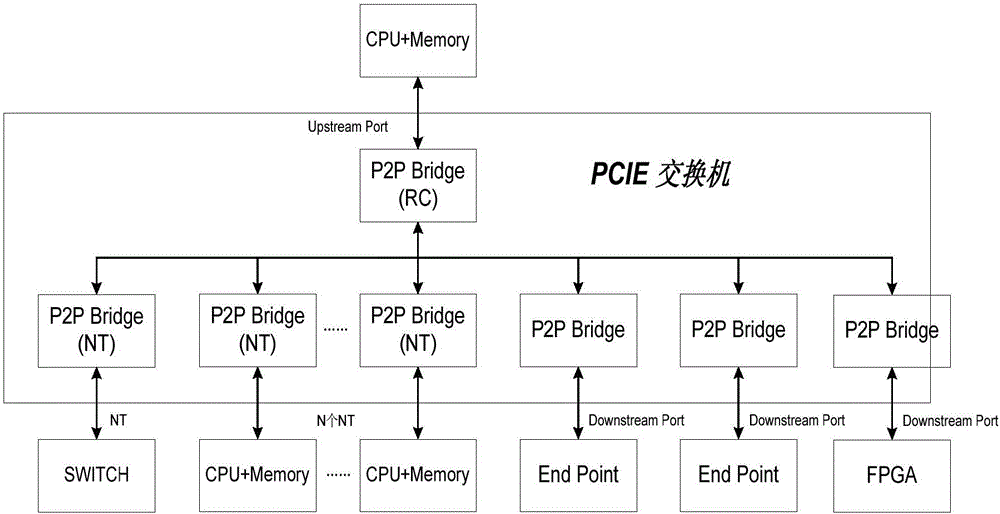

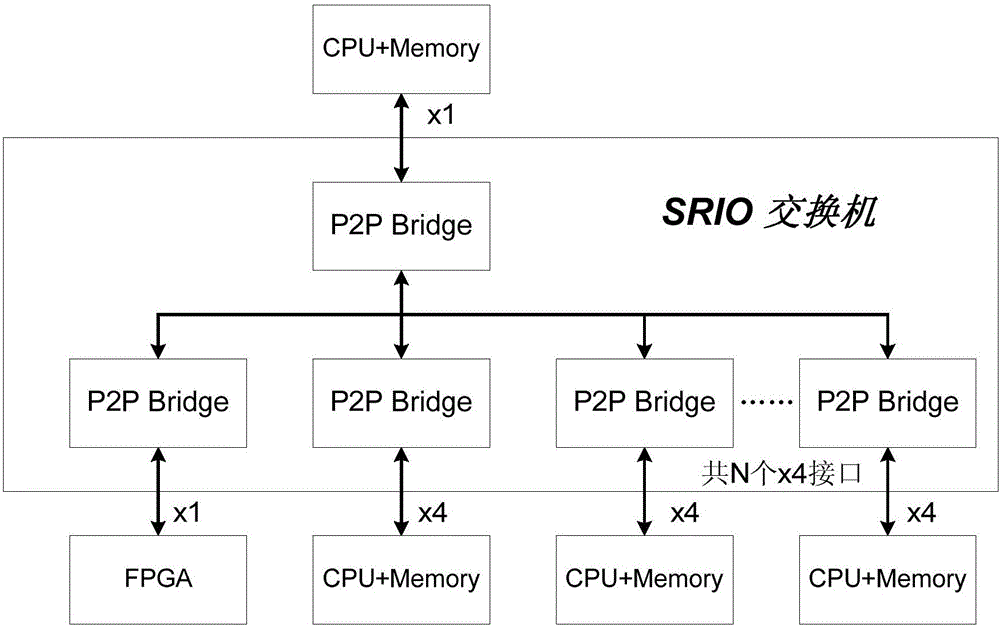

[0018] Combine below figure 1 The block diagram of the VPX architecture shown, figure 2 The schematic block diagram of the PCIE switching network shown, image 3 The block diagram of the SRIO switching network shown and Figure 4 The schematic block diagram of the B code time synchronization method shown further describes the method of the present invention.

[0019] Such as figure 1 As shown, the VPX architecture consists of N blades, two switching boards, switching modules, and power boards. Among them, the blade provides computing resources for the system and realizes load balancing based on virtualization; the switching board can realize switching functions such as Ethernet, PCIE, and SRIO; the switching board can realize KVM switching; the power board configures different power supplies for each module. The management chip intelligently manages the power board.

[0020] Such as figure 2 As shown, the PCIE switch is realized by using a high-performance PCI-E switch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com