Bus fault injection system based on DSP and FPGA

A technology for injecting system and bus faults, applied in faulty hardware testing methods, detecting faulty computer hardware, instruments, etc., can solve problems such as incomplete coverage of signal fault injection, achieve good visual interface, strong flexibility, and simplify circuits The effect of the design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

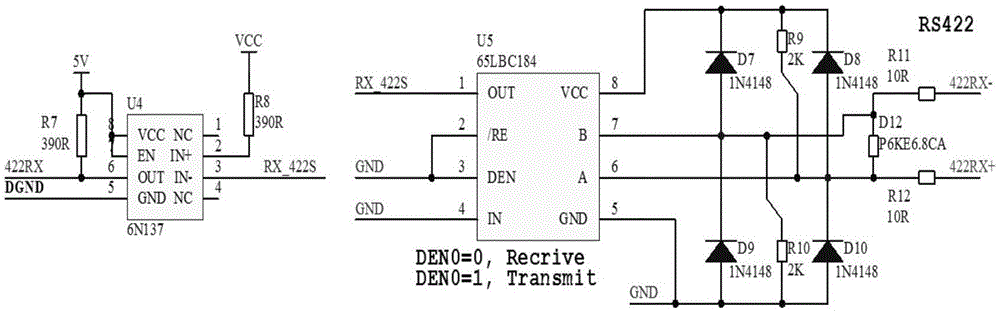

[0033] Such as figure 1 As shown, the bus fault injection system based on DSP and FPGA can configure the required fault mode through the fault injection unit connected to the bus system without changing the signal of the test equipment and the device under test that provide the excitation source , change the communication signal, and realize the function of adding various faults in real time in the normal communication of the bus equipment.

[0034] Such as figure 2 and Figure 7 , the bus fault injection system based on DSP and FPGA includes two parts, the upper computer and the lower computer. The upper computer uses KingView to design and provide a human-computer interaction interface, which is used to receive the fault command issued by the operator and send the fault command to the lower machine. After the lower computer is powered on, first initialize the DSP, FPGA, W5300, etc., then set the serial signal receiving baud rate according to the actual communication baud...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com