Preparation method for VDMOS integrated ESD structure

An epitaxial layer and process technology, which is applied in the field of preparation of VDMOS integrated ESD structures, can solve problems such as increased step difference, process difficulty, and large step height difference, and achieves reduced step height difference, convenient process, and improved device durability. pressure effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

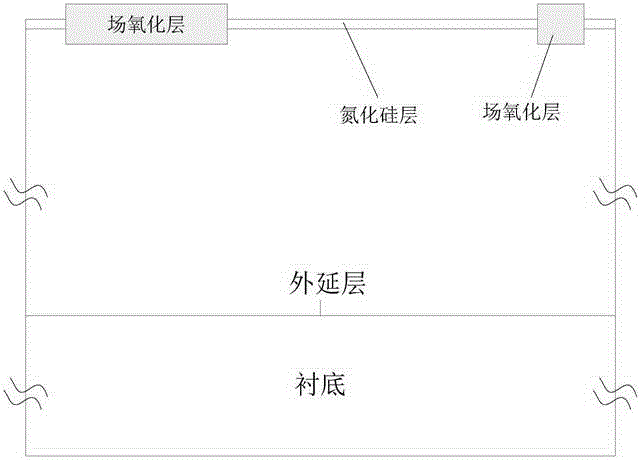

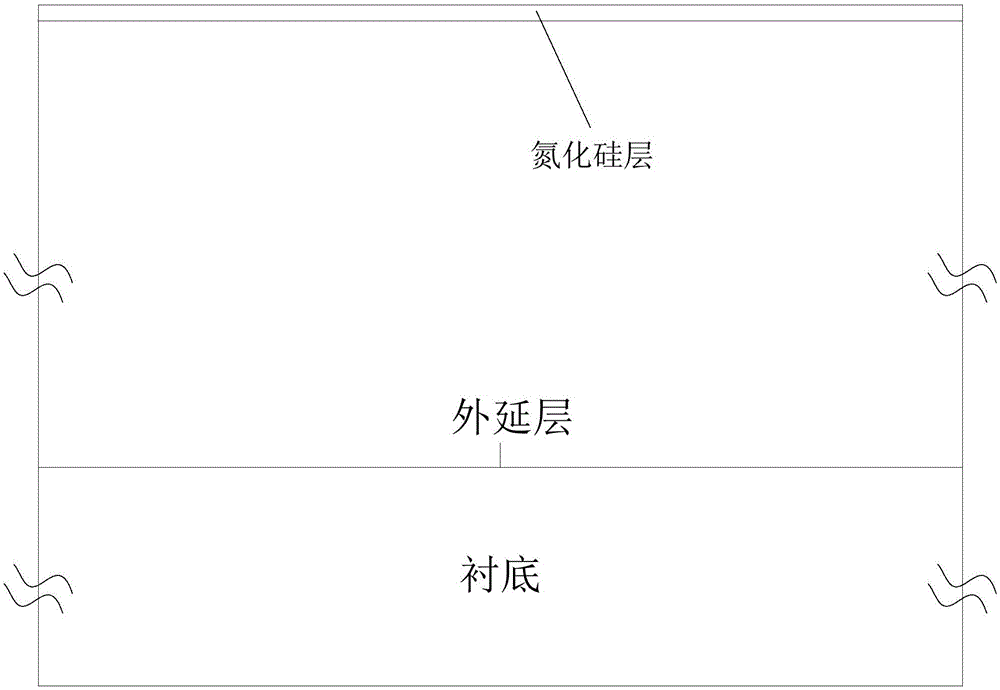

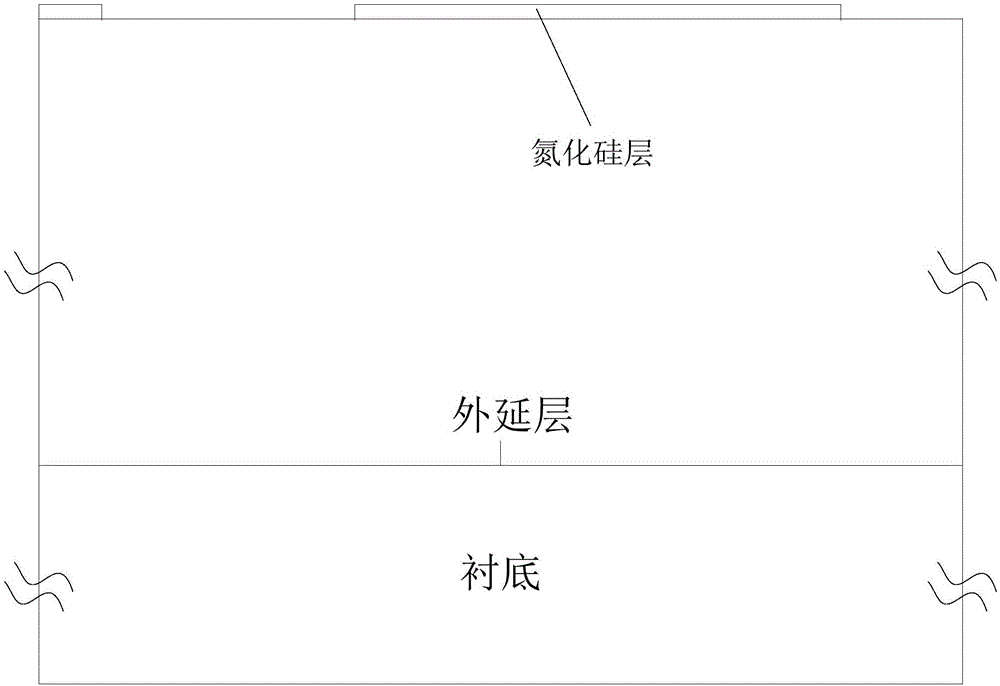

[0040] An embodiment of the present invention is a method for preparing a VDMOS integrated ESD structure. The method is: forming a pattern by silicon nitride deposition and photolithography etching, growing a field oxide layer in the area where the epitaxial layer is exposed after the silicon nitride is etched away, and then The ESD structure is completed in the follow-up and traditional VDMOS process.

[0041] The embodiment of the present invention provides a method for preparing a VDMOS integrated ESD structure, the method is realized through the following steps:

[0042] Step 1: Provide an n-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com