MOS transistor forming method

A technology of MOS transistors and transistors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of poor performance and reliability of MOS transistors, reduce junction capacitance, suppress hot carrier injection effects and strike wear effect, performance-enhancing effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The performance and reliability of the MOS transistors formed in the prior art are poor as the feature size is further reduced.

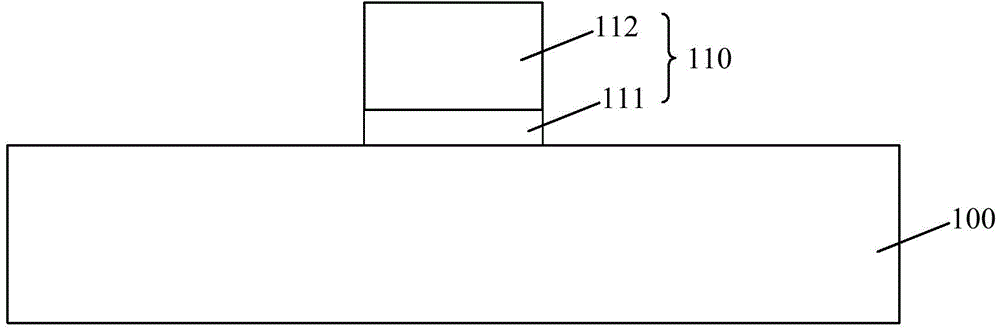

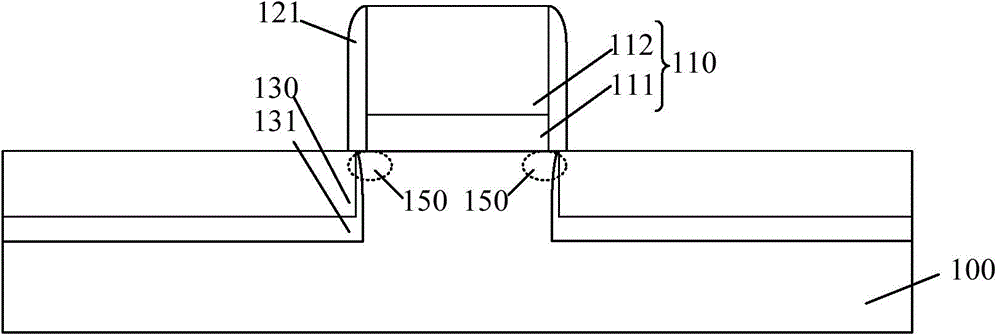

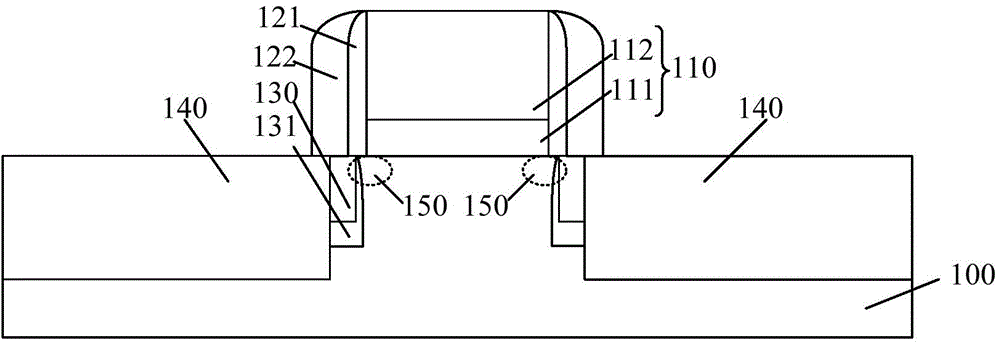

[0034] Figure 1 to Figure 4 It is a schematic cross-sectional structure diagram of the formation process of the MOS transistor in an embodiment of the present invention.

[0035] refer to figure 1 , providing a semiconductor substrate 100, forming a gate structure 110 on the surface of the semiconductor substrate 100, the gate structure 110 including a gate dielectric layer 111 on the surface of the semiconductor substrate 100 and a gate electrode layer 112 on the surface of the gate dielectric layer 111 .

[0036] refer to figure 2 , forming an offset spacer 121 on the sidewall surface of the gate structure 110 .

[0037] Please still refer to figure 2 , using the offset spacer 121 and the gate structure 110 as a mask, perform lightly doped drain implantation to the semiconductor substrate 100 on both sides of the gate structure 110 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com