A Method of Using Compiler to Automatically Generate Width-Configurable Bus Layout

An automatic generation and compiler technology, applied in the direction of instruments, special data processing applications, calculations, etc., can solve the problems of time-consuming and labor-intensive, lack of flexibility and configurability, etc., to improve flexibility, save manpower and time, and reduce duplication. design effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

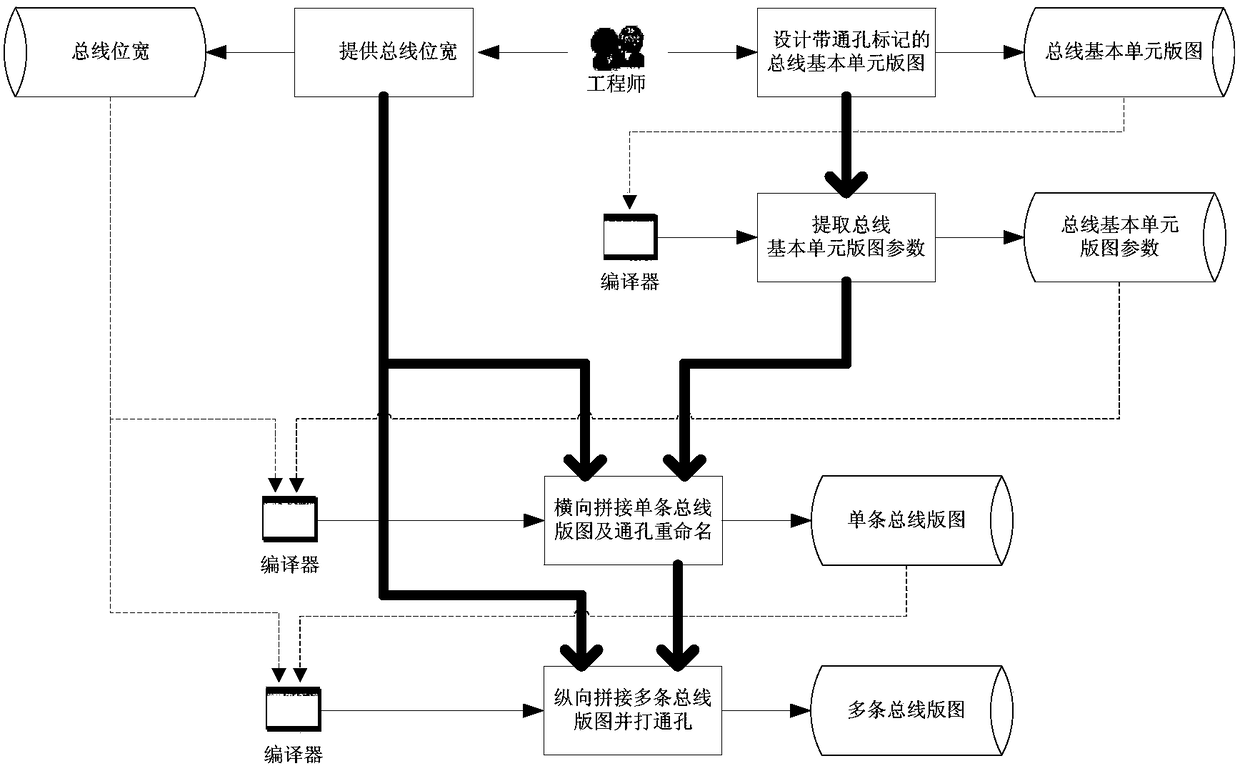

[0023] The present invention uses a compiler to automatically generate a method for a bus layout with configurable bit width, such as figure 2 As shown, it specifically includes the following steps.

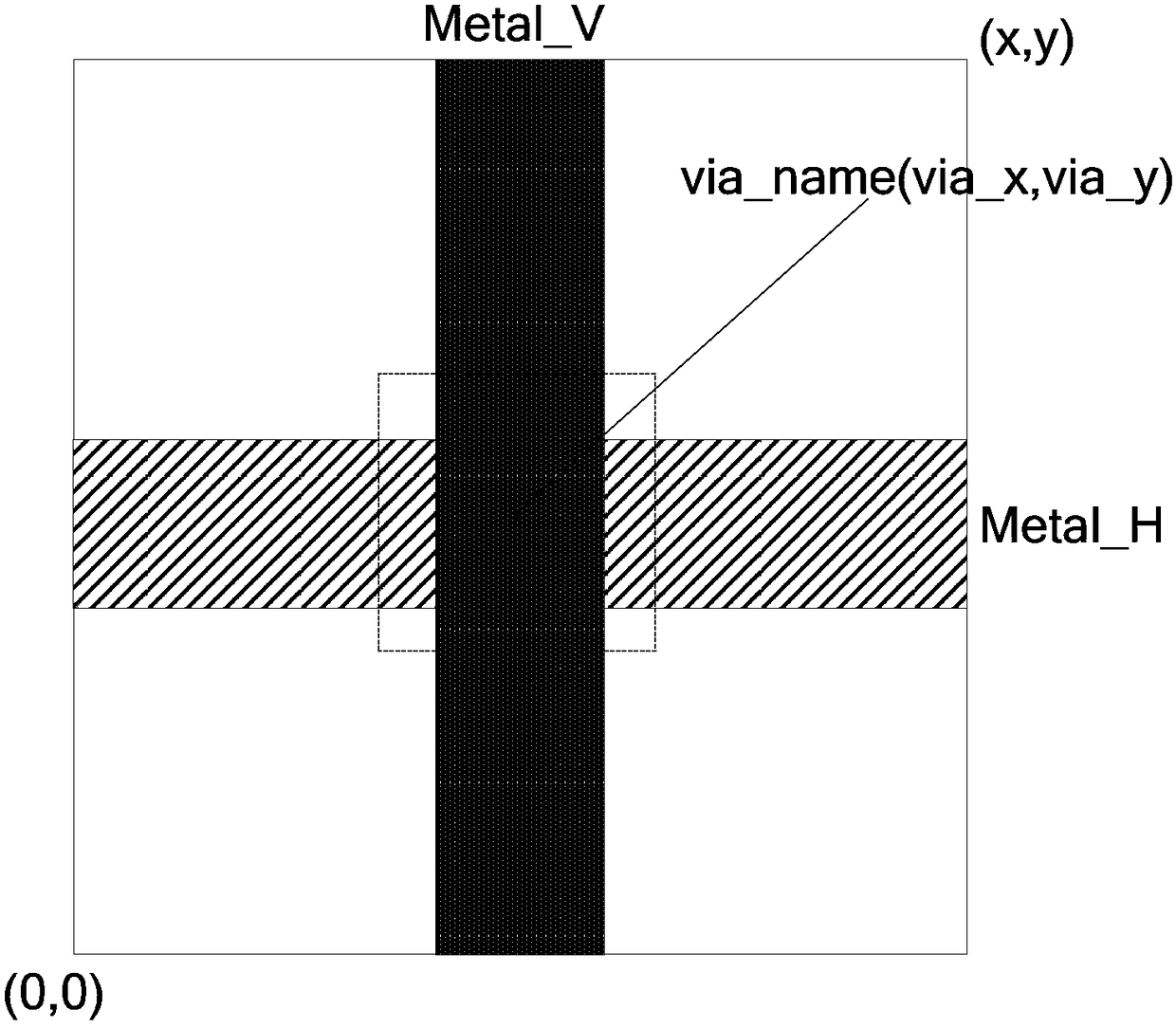

[0024] The first step is to design the layout of the basic unit of the bus by the engineer, and add information recognizable to the compiler such as the boundary of the layout unit, the name of the via, and the coordinates of the via to the layout; the engineer provides the bus bit width n that the compiler needs to generate; Among them such as image 3 As shown, the marking information of the basic unit layout of the bus includes the via name and coordinates via_name(via_x, via_y); it includes the horizontal metal pattern Metal_H, the vertical metal pattern Metal_V, the name of the vi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com