Time domain interleaving analog-digital converter sample time mismatch calibration method and system

An analog-to-digital converter, sampling time technology, applied in the direction of analog-to-digital converter, analog-to-digital conversion, code conversion, etc., can solve the problems of limited calibration accuracy of differentiators, insensitivity to gain mismatch, and increased circuit complexity. , to achieve the effect of high calibration accuracy, simple and easy circuit structure, and avoidance of amplitude errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The technical solution of the present invention will be further introduced below in combination with specific embodiments.

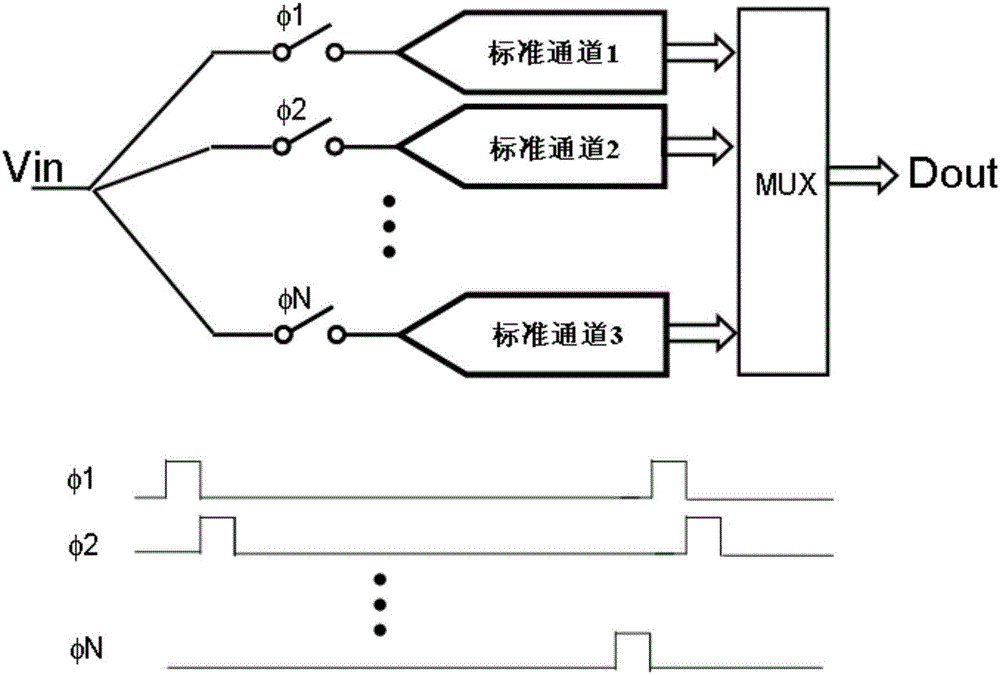

[0039] The invention discloses a method for calibrating the sampling time mismatch of a time-domain interleaved analog-to-digital converter, which includes the following steps:

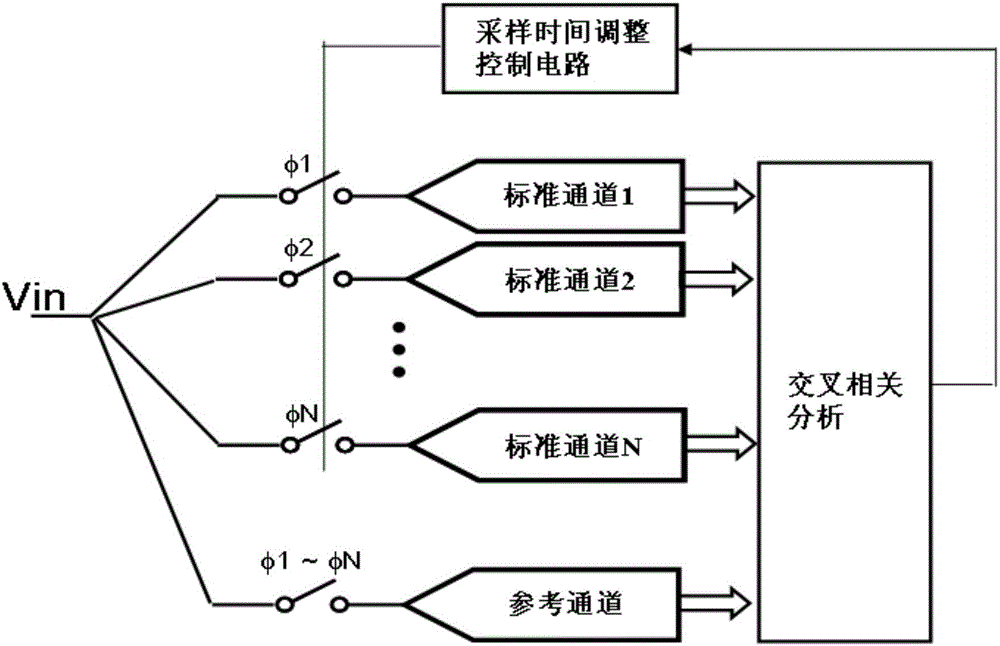

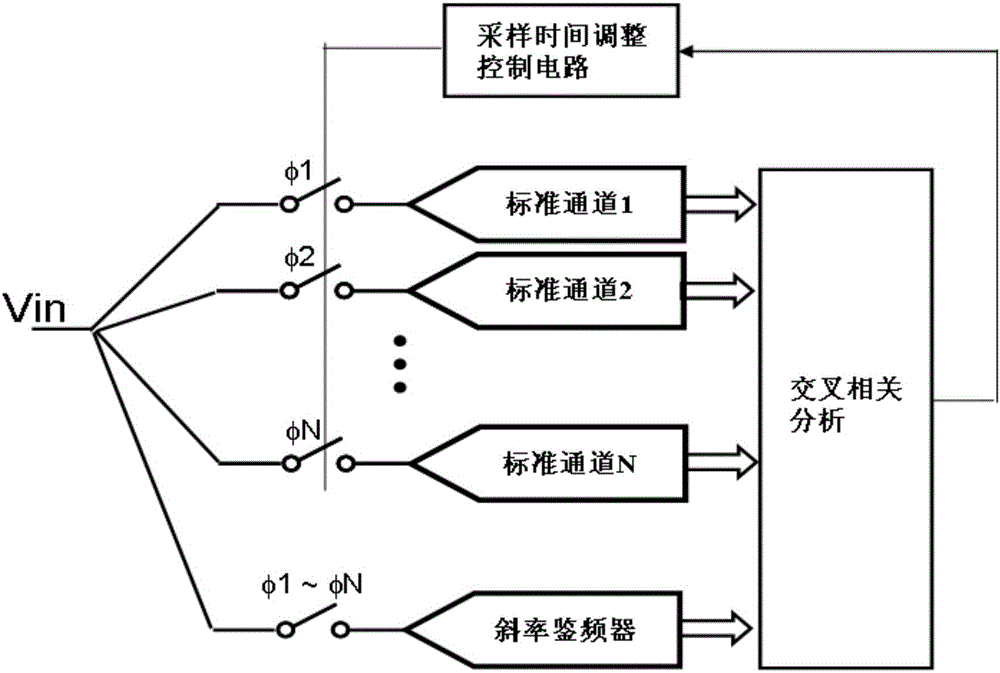

[0040] S1: Add a reference channel in addition to the N standard channels of the analog-to-digital converter to form a total of N+1 channels;

[0041] S2: The output data of each channel is sent to the sampling time mismatch coefficient extraction circuit 1, and the control coefficient of the adjustment circuit is extracted and sent to the sampling time adjustment control circuit 2;

[0042] The adjustment circuit control coefficient is calculated by formula (1):

[0043] CTS k+1 =CTS k -u*(e k -e k-1 )*sign(CTS k -CTS k-1 ) (1)

[0044] In formula (1), CST is the control coefficient of the adjustment circuit, u is the iterative step coefficient of the approximati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com