Film transistor and preparation method thereof, array substrate and display panel

A thin-film transistor and thin-film technology, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, nanotechnology for materials and surface science, etc., can solve the problem that the active layer is easy to be corroded, so as to avoid defective devices and realize simple process , The effect of simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

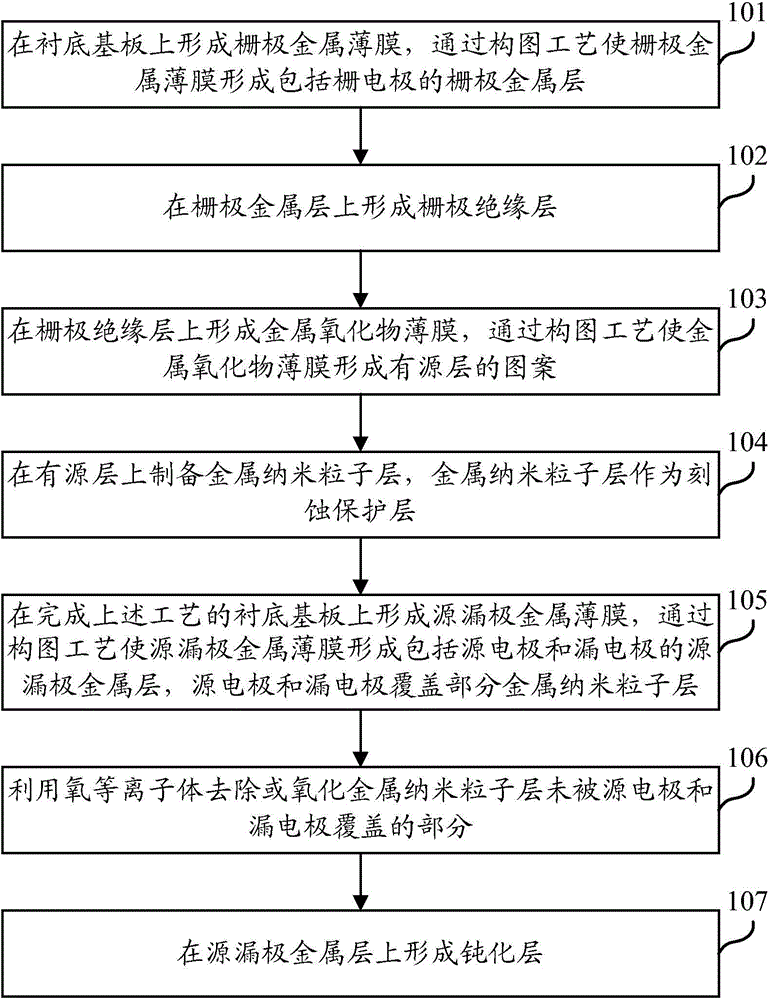

[0051] see figure 1 , an embodiment of the present invention provides a method for manufacturing a thin film transistor, including:

[0052] 101. Form a gate metal thin film on a base substrate, and form the gate metal thin film into a gate metal layer including a gate electrode through a patterning process.

[0053] Depending on the specific application of the metal oxide thin film transistor, a glass substrate with a buffer layer can be used as the base substrate, or a flexible substrate with a water-oxygen barrier layer can be used as the base substrate, preferably, polyethylene naphthalate Glycol ester, polyethylene terephthalate, polyimide, or metal foil are used as materials for the flexible substrate.

[0054] Preferably, a single-layer film or a composite composed of at least two or more of aluminum thin films, copper thin films, molybdenum thin films, titanium thin films, silver thin films, gold thin films, tantalum thin films, tungsten thin films, chromium thin film...

Embodiment 1

[0073] The embodiment of the present invention provides a first specific method for preparing a metal oxide thin film transistor, including:

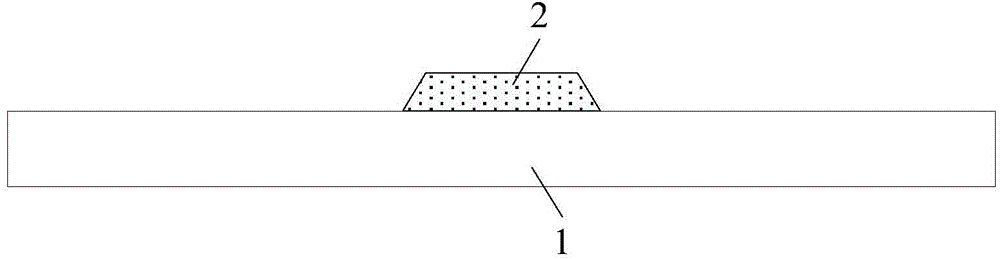

[0074] Step 1: Deposit a molybdenum / aluminum / molybdenum three-layer metal film on the base substrate 1 as a gate metal film, and the thickness of the molybdenum / aluminum / molybdenum three-layer metal film is 25 / / 100 / 25 nanometers respectively , the gate metal film is formed into the gate electrode 2 through a patterning process. Substrate substrate 1 is S with a thickness of 200 nanometers i o 2 The buffer layer is an alkali-free glass substrate. The schematic diagram after preparing the gate electrode 2 on the base substrate 1 is as follows figure 2 shown.

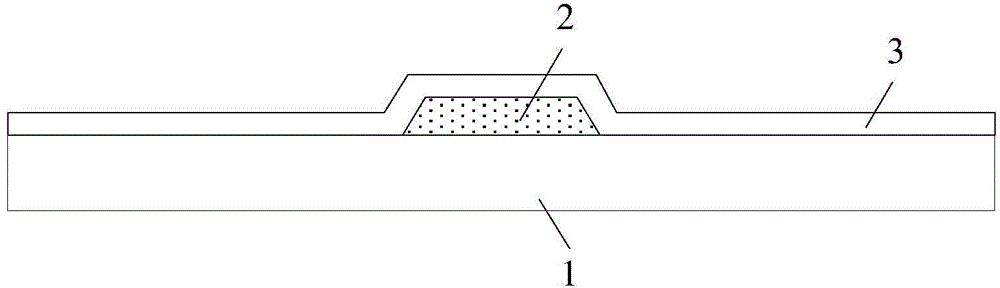

[0075] In step 2, a gate insulating layer 3 is deposited on the base substrate 1 after the above steps by using a plasma-enhanced chemical vapor deposition method. The schematic diagram after the gate insulating layer 3 is prepared is as follows: image 3 shown.

[0076] The...

Embodiment 2

[0087] The embodiment of the present invention provides a second specific method for preparing a metal oxide thin film transistor, including:

[0088] Step 1: On the base substrate 1, a copper metal film is deposited as a gate metal film by physical vapor deposition. The thickness of the copper metal film is 500 nanometers, and the gate metal film is formed into a gate electrode 2 through a patterning process. The base substrate 1 is Al with a thickness of 50 nanometers 2 o 3Flexible substrate for water and oxygen barrier layer. The schematic diagram after preparing the gate electrode 2 on the base substrate 1 is as follows figure 2 shown.

[0089] In step 2, a gate insulating layer 3 is deposited on the base substrate 1 after the above steps by using a plasma-enhanced chemical vapor deposition method. The schematic diagram after the gate insulating layer 3 is prepared is as follows: image 3 shown.

[0090] The gate insulating layer 3 is formed by stacking aluminum oxi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com