Single Event Toggle Soft Error Detection Method for FPGA Based on Redundant Interconnection Resources

A single-event flipping and interconnection resource technology, which is applied in the field of FPGA single-event flipping soft error detection based on redundant interconnection resources, can solve problems such as inability to realize double backup and unbalanced resource occupation, and achieve efficient online detection, high-efficiency Effect of Redundant Interconnect Resource Search Algorithm

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

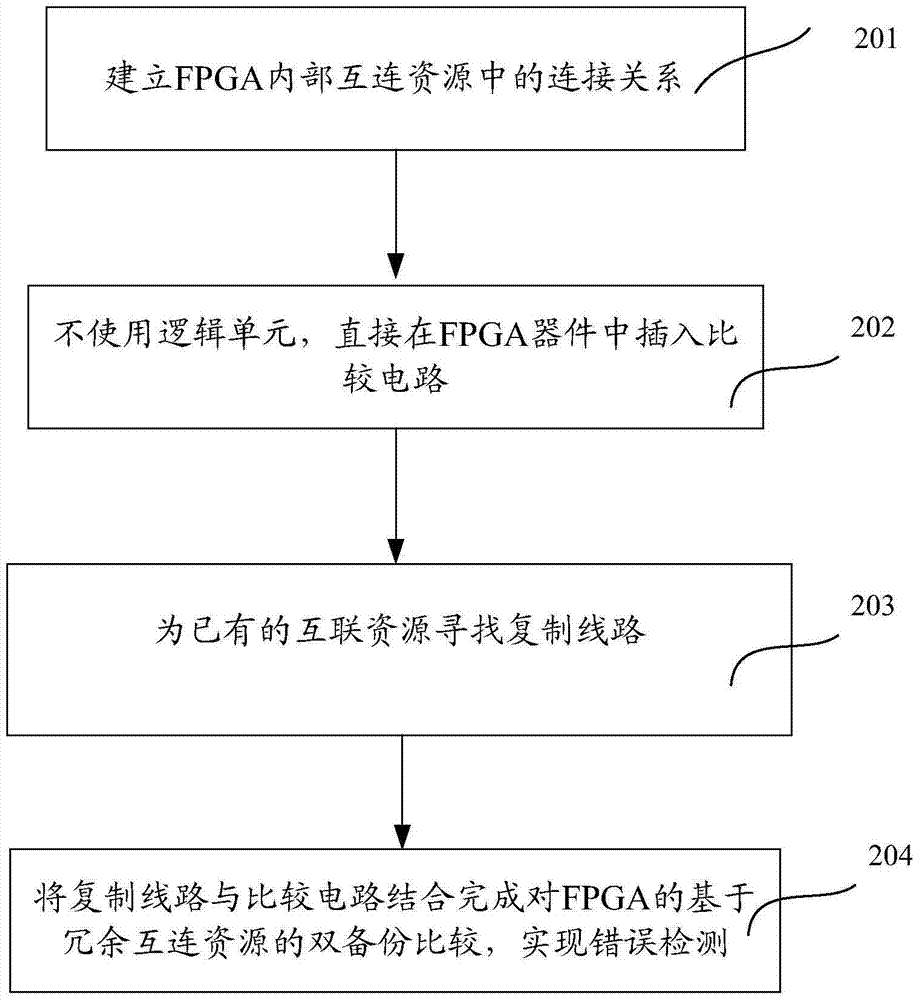

Method used

Image

Examples

Embodiment Construction

[0037] The embodiments of the present invention will be described below through specific examples and in conjunction with the accompanying drawings, and those skilled in the art can easily understand other advantages and effects of the present invention from the contents disclosed in this specification. The present invention can also be implemented or applied through other different specific examples, and various details in this specification can also be modified and changed based on different viewpoints and applications without departing from the spirit of the present invention.

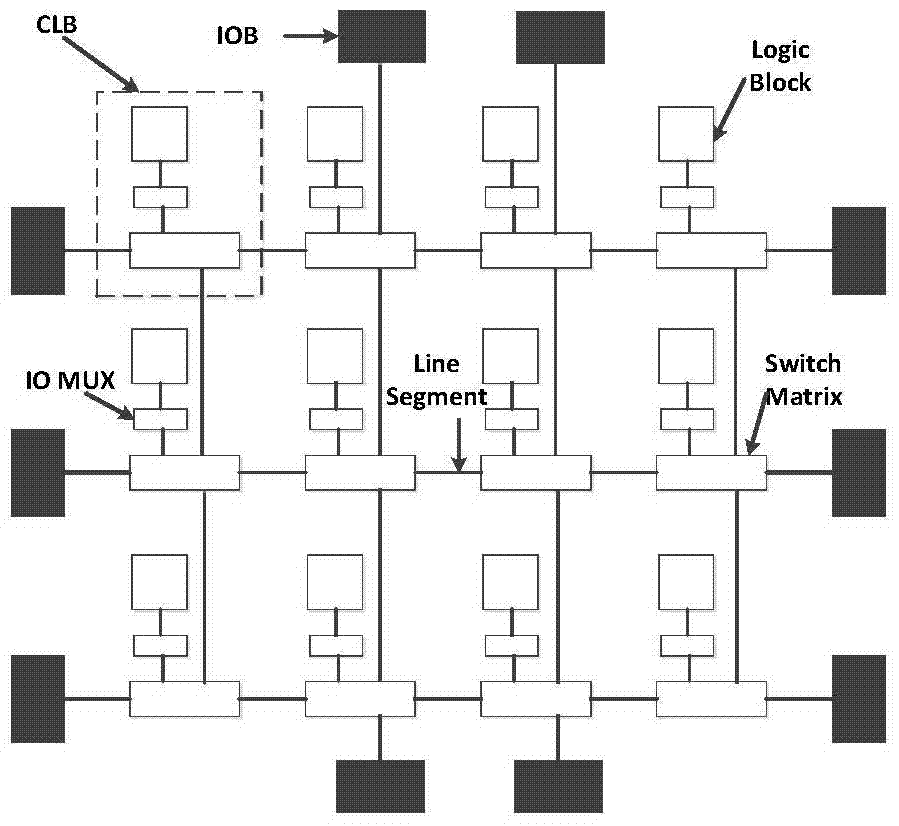

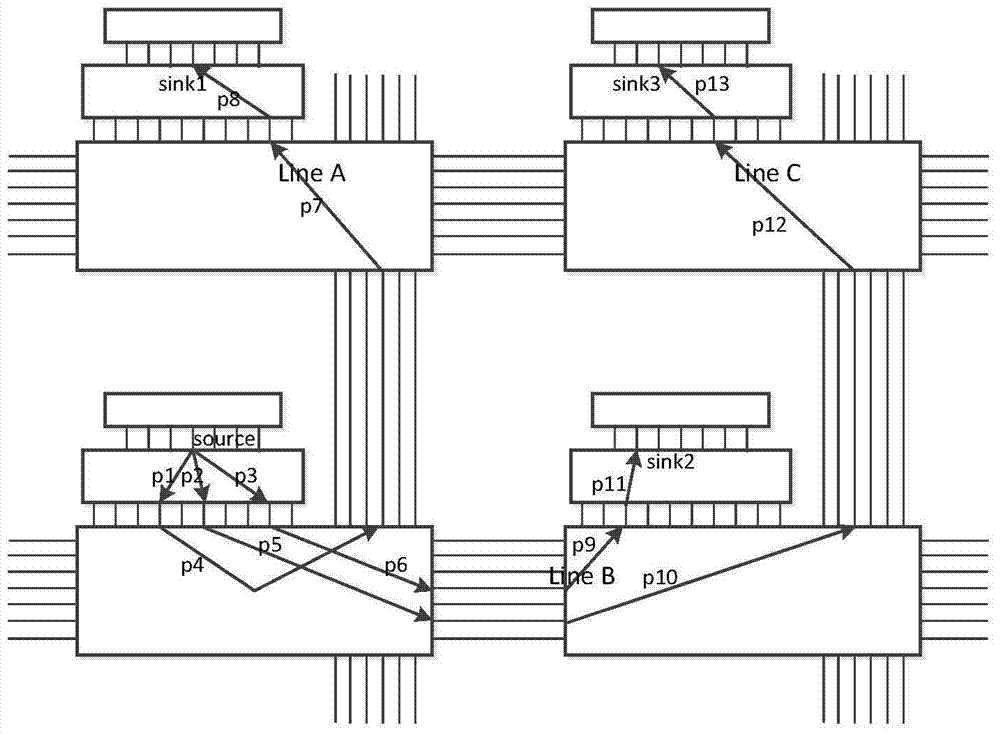

[0038] The FPGA device that the present invention faces is the Virtex series FPGA device of Xilinx Company, and its specific structure diagram is as follows figure 1 shown. The Virtex device adopts an island structure, which is mainly composed of a configurable logic module array CLB, and the CLB is surrounded by an IO module IOB. Each CLB is composed of a logic block (Logic block, LB), an input an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com