FPGA-based IRIG-B code decoder and decoding method thereof

A decoder and B code technology, applied in FPGA-based IRIG-B code decoder and its decoding field, can solve the problems of affecting micro-processing response and taking up a large processing time, so as to improve efficiency and pertinence, reduce noise, Effect of improving precision of judgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

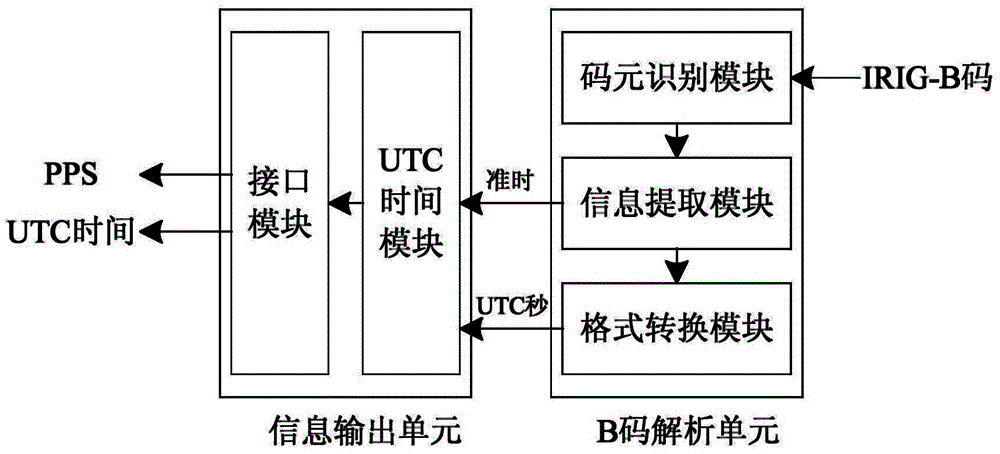

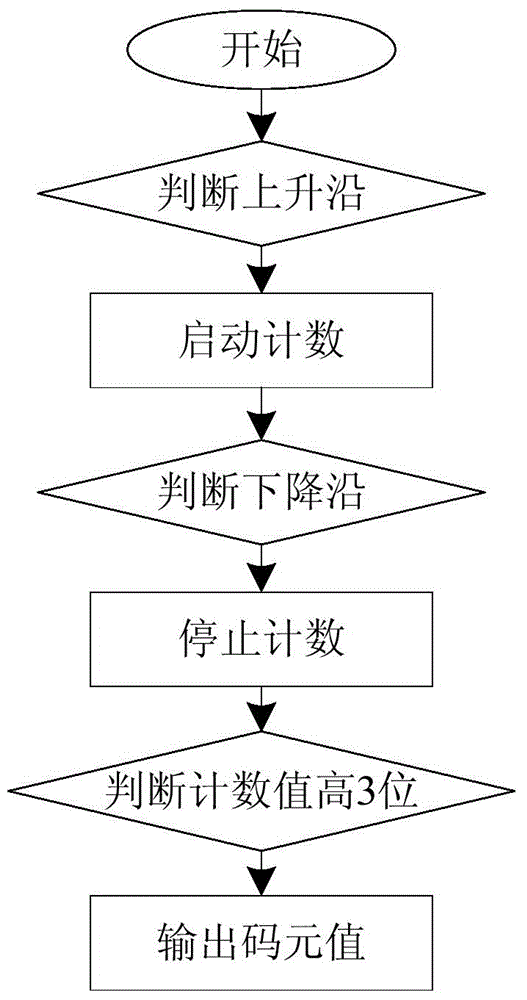

[0030] A kind of FPGA-based IRIG-B code decoder of the present invention, as figure 1 As shown, it includes a B code analysis unit and an information output unit arranged in the FPGA; the B code analysis unit includes a symbol identification module, an information extraction module and a format conversion module connected in sequence, and the information output unit includes a UTC time module connected in sequence and interface module; the code element identification module is used to process the IRIG-B code signal of external input; the information extraction module is used to receive the code element type output by the symbol identification module, and provides the punctual reference point signal to the UTC time module; the format conversion module It is used to provide the UTC second signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com