Off-chip accelerator applicable to fusion memory of 2.5D (2.5 dimensional) multi-core system

A multi-core system and memory technology, applied in the field of off-chip accelerator structure, can solve the problems of low communication efficiency and large communication delay between chips, and achieve the effect of avoiding design, avoiding performance and power loss, and reducing design complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

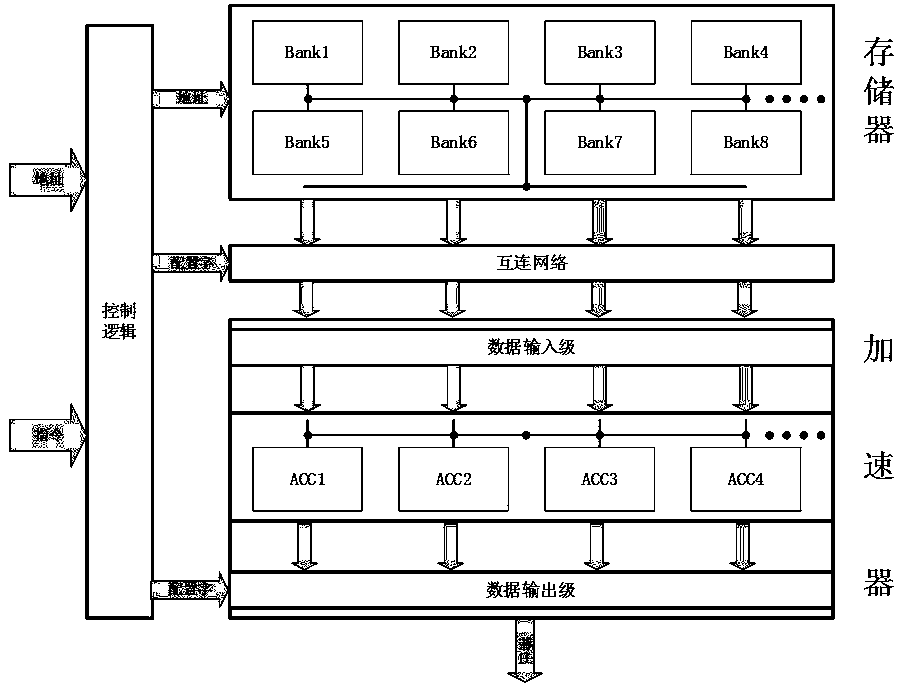

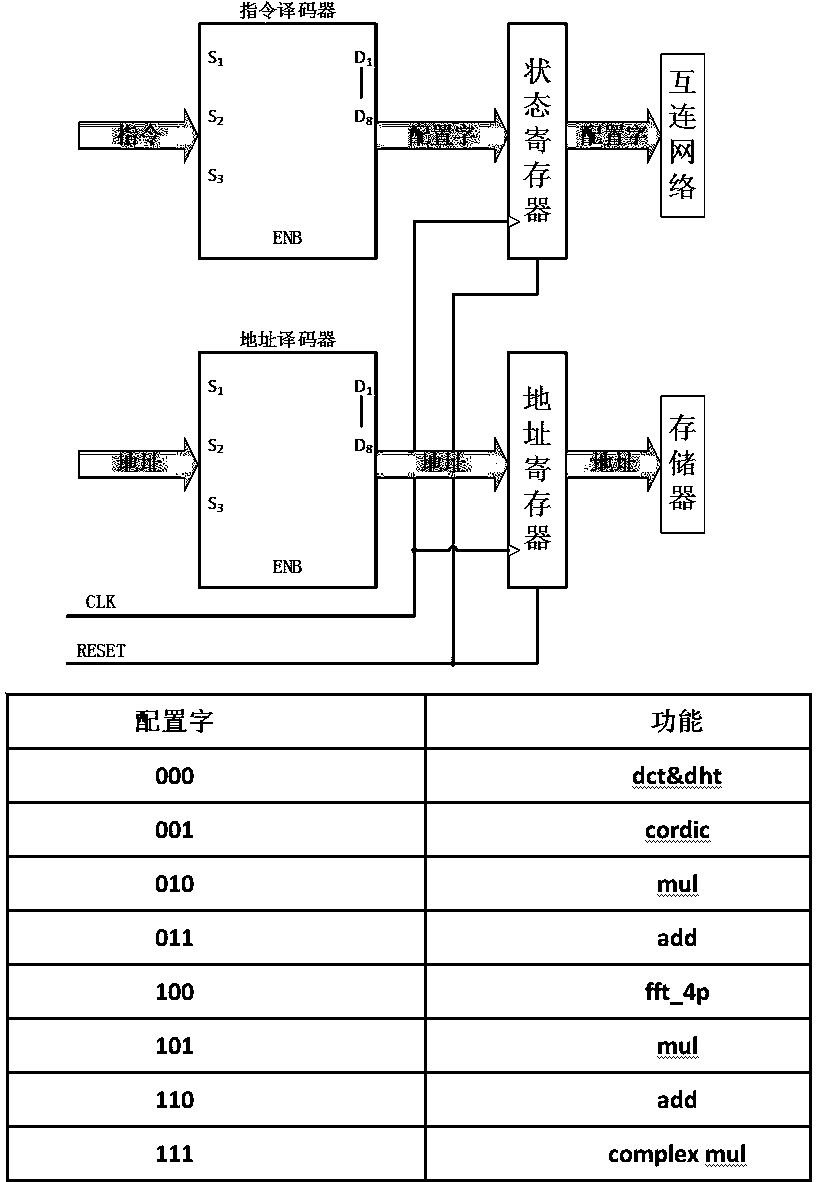

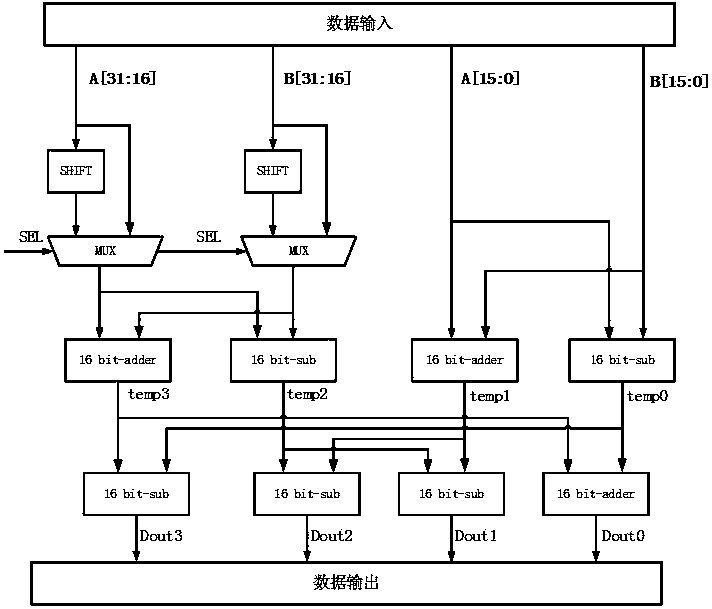

[0023] Such as figure 1 As shown, the structure of the fusion accelerator and memory proposed by the present invention is implemented on one chip in a highly integrated manner. The memory and the accelerator are connected together in a certain coupling way through interconnection. The processor sends data, address and configuration packets to the control logic through the interconnection channel between chips. The control logic decodes the configuration word according to the information in the instruction, and configures The word will be written into the status register immediately and saved, and it will be kept in the whole computing cycle until the arrival of the next configuration word. The output of the status register is directly connected to the interconnection network. The data in the memory flows along the configured interconnection network. You can choose to directly return to the processor without any processing, or you can choose to enter some kind of accelerator, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com