Semiconductor chips and semiconductor devices

A semiconductor and chip technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as increased wiring impedance, decreased wiring performance, and increased size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0206] [Embodiment 1]

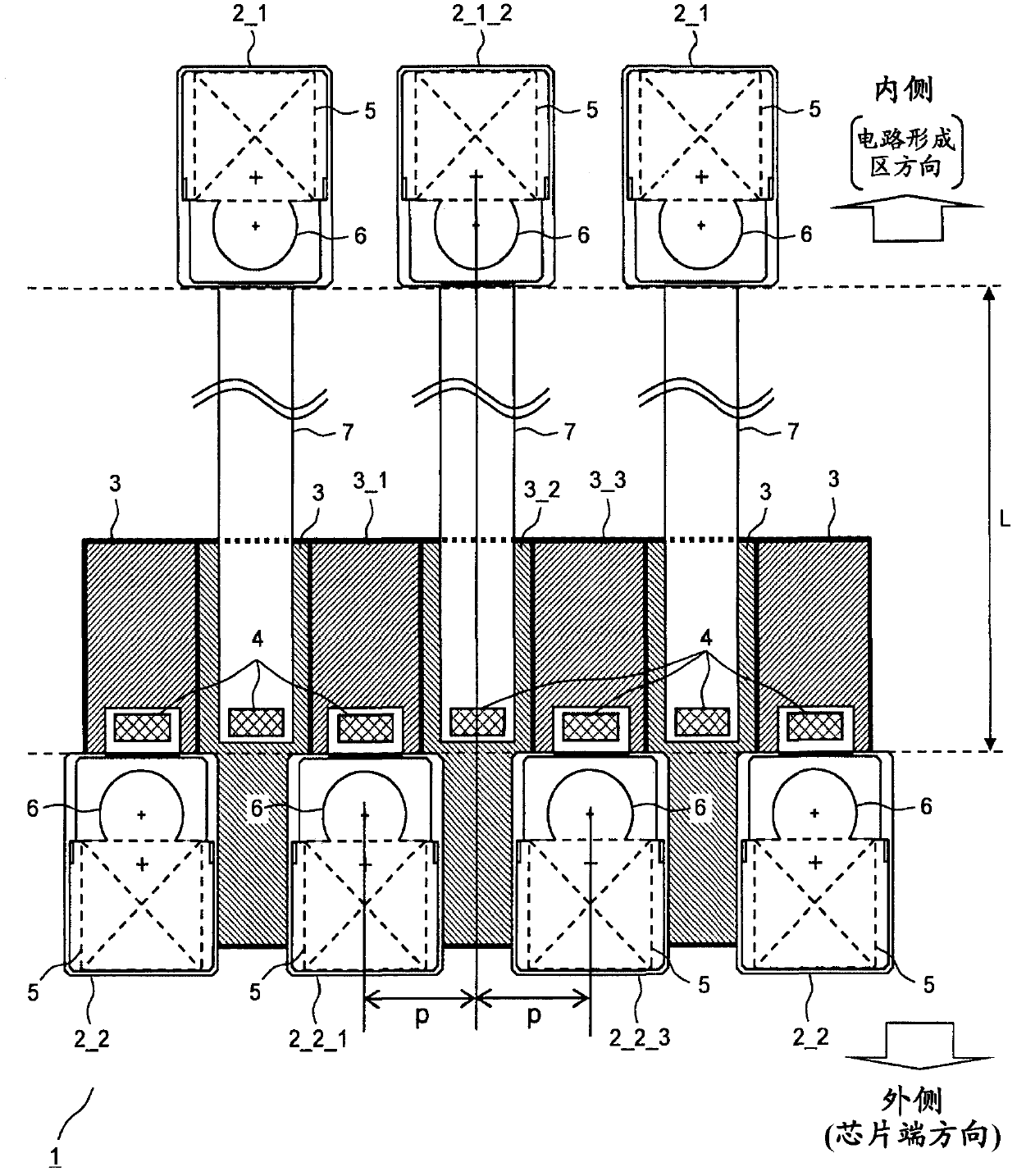

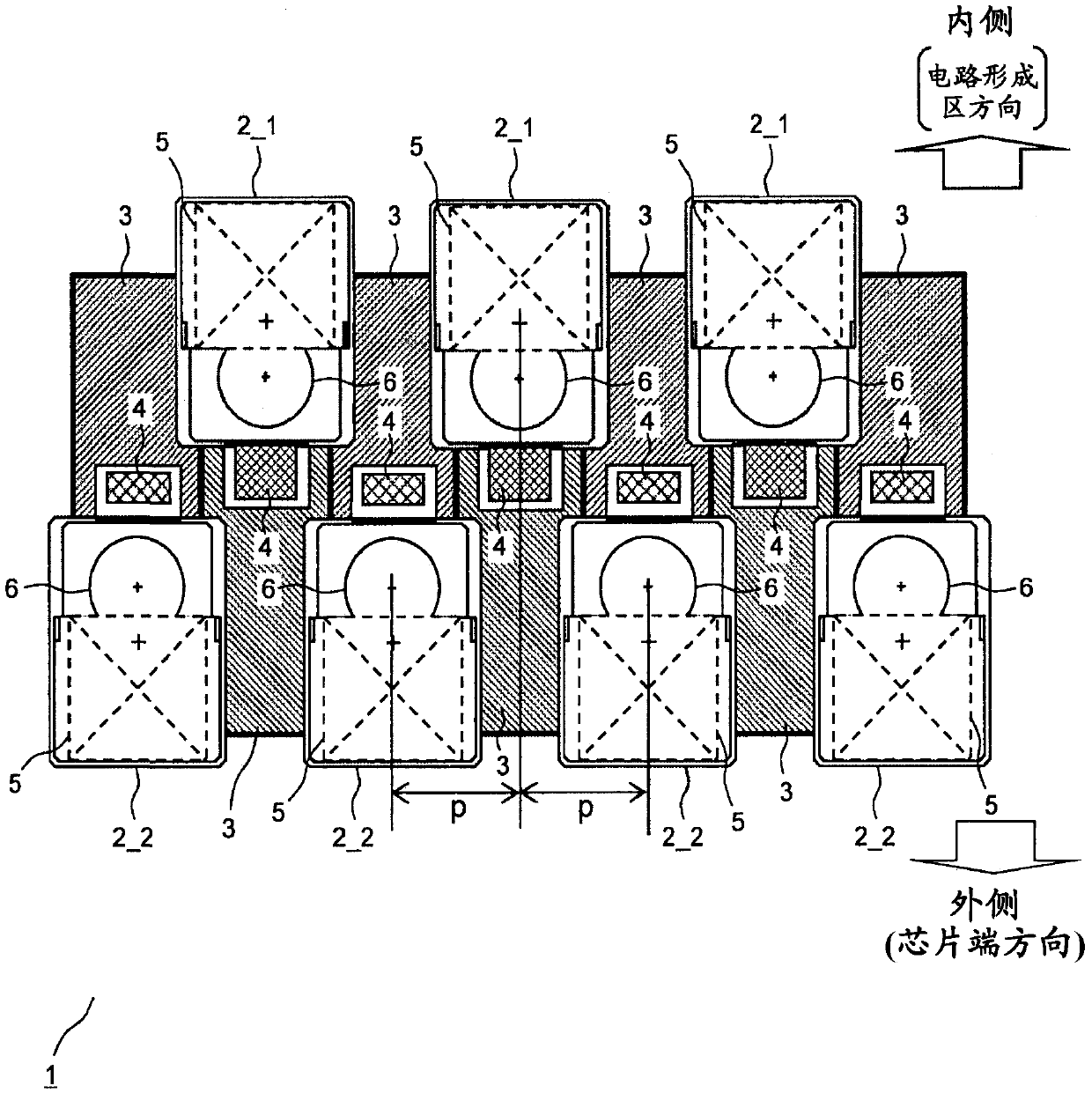

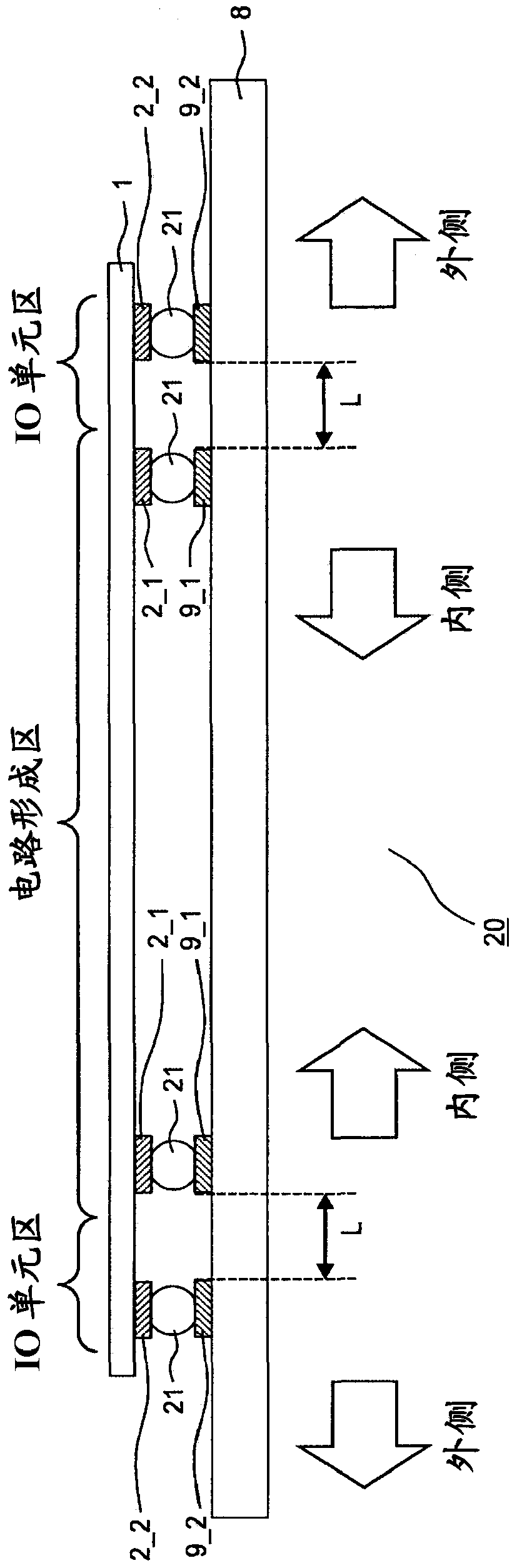

[0207] figure 1 is a layout diagram showing the arrangement of the pads 2 in the semiconductor chip 1 of Embodiment 1, figure 2 It is a layout diagram showing the arrangement of pads in a conventional semiconductor chip. image 3 It is a schematic diagram showing the mounting state in the cross-sectional direction of the semiconductor device 20 in which the semiconductor chip 1 of Embodiment 1 is flip-chip mounted on the substrate 8, Figure 4 It is a schematic diagram showing the arrangement of the pads 2 in the semiconductor chip 1 of Embodiment 1 and Embodiment 2 and the arrangement of the substrate pads 9 in the substrate 8 on which it is flip-chip mounted.

[0208] The semiconductor device 20 of the first embodiment is like image 3 As shown, a semiconductor chip 1 is flip-chip mounted on a substrate 8 to form a configuration. The semiconductor chip 1 has die pads 2_1 and 2_2 ; the substrate 8 has substrate pads 9_1 and 9_2 respect...

Embodiment approach 2

[0225] [Embodiment 2]

[0226] For the prescribed method for the predetermined distance L, reference Figure 9 Description and Reference Figure 5 The illustrated example differs from the example. The same applies to the predetermined distance L in consideration of the wiring properties in the substrate 8 on which the semiconductor chip 1 is flip-chip mounted, but it is also specified in consideration of the wiring properties of the plated wiring.

[0227] Other configurations are the same as those described in Embodiment 1. against figure 1 , image 3 , Figure 4 The descriptions above are also applicable to Embodiment 2.

[0228] Figure 9 It is a layout diagram showing the arrangement of substrate pads 9_1 and 9_2 in substrate 8 on which semiconductor chip 1 of Embodiment 2 is flip-chip mounted.

[0229] In the substrate 8, an inner substrate pad row consisting of a plurality of substrate pads 9_1 connected to the inner pad row of the semiconductor...

Embodiment approach 3

[0233] [Embodiment 3]

[0234] Embodiments 1 and 2 show an example in which the probe region 5 and the bonding region 6 are provided on the same die pad. Here, since the probing area 5 is used to apply a test signal or observe an output signal in the test of the semiconductor chip 1 as described above, and is used for contact with the probe, it is pressed against the probe during the test. while applying pressure. In the conventional semiconductor chip, it can be arranged in the area of the input / output unit 3 or on the gap area with the internal circuit, so the pressing by the probe does not affect the internal circuit. However, as described in Embodiments 1 and 2, since the inner pad row is moved toward the inner side, that is, toward the circuit formation region, there is a possibility that the inner pad row is arranged on the internal circuit. In this case, the pressure by the probe affects the characteristics and operation of the internal circuit, making it diffi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com