SIP (system in package) chip testing platform and method

A chip test and chip technology, applied in the field of SIP chip test platform, can solve problems such as complex operation, failure to troubleshoot problems, and inability to fully guarantee performance, and achieve the effects of easy operation, low development cost, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

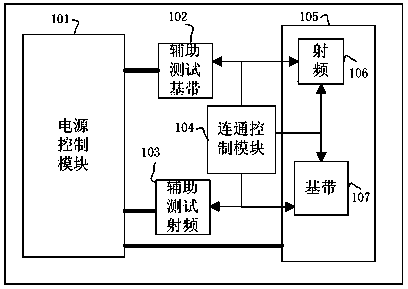

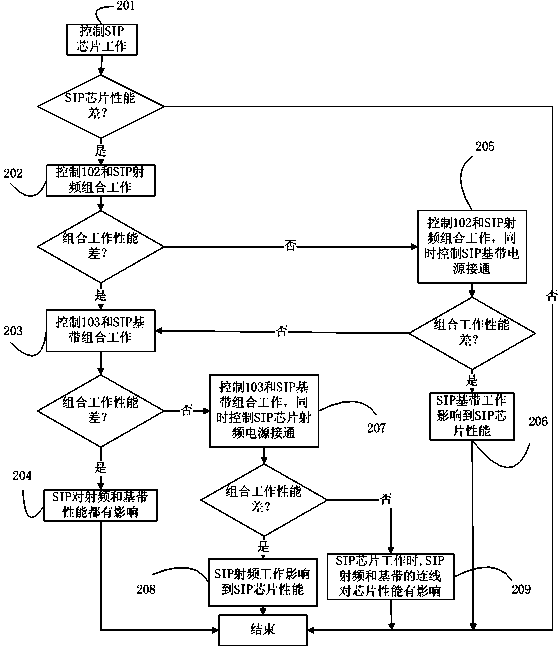

[0019] The basic principle of the test method of this test platform is as follows: First, conduct a comprehensive evaluation of the combined work of the baseband and radio frequency chips before packaging, test the overall performance of a single baseband and radio frequency combination, and record the performance of the test in detail. The test performance is used as the performance test benchmark after SIP encapsulation. When testing the SIP-encapsulated chip, the tests performed using this test platform will record the corresponding performance parameters, and compare with the performance before...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com