On-chip communication method and on-chip communication device on basis of three physical interconnection lines for integrated circuits

A technology of integrated circuits and communication methods, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of low power consumption management technologies such as many physical connections of the DCR bus, inaccessibility of slave devices, and failure to support device power-off, etc., to achieve Less hardware resources and physical implementation costs, less global wiring resource occupation, and flexible power-off strategies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

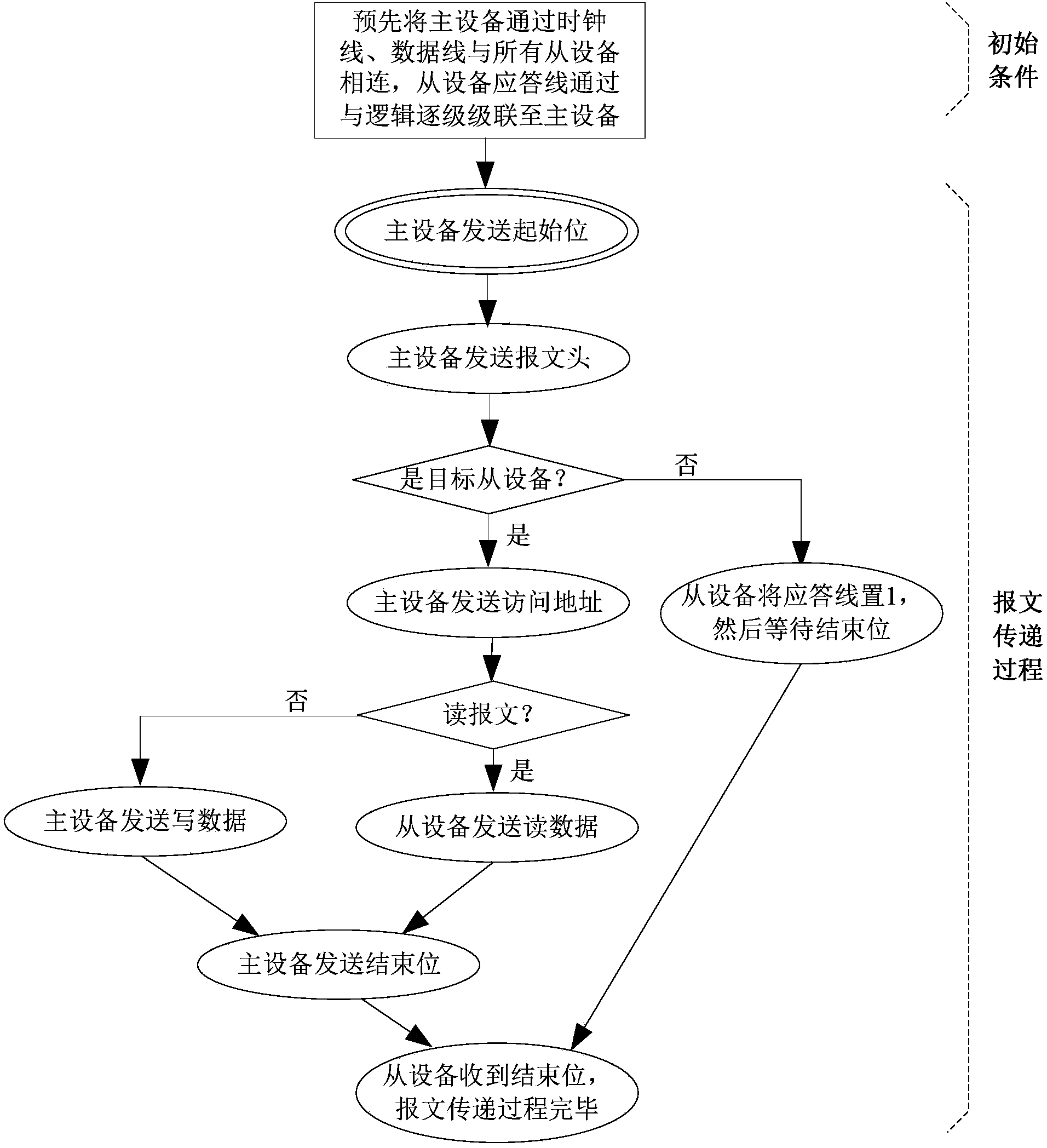

[0029] Such as figure 2 As shown, the implementation steps of the integrated circuit on-chip communication method based on three physical interconnection lines in this embodiment are as follows:

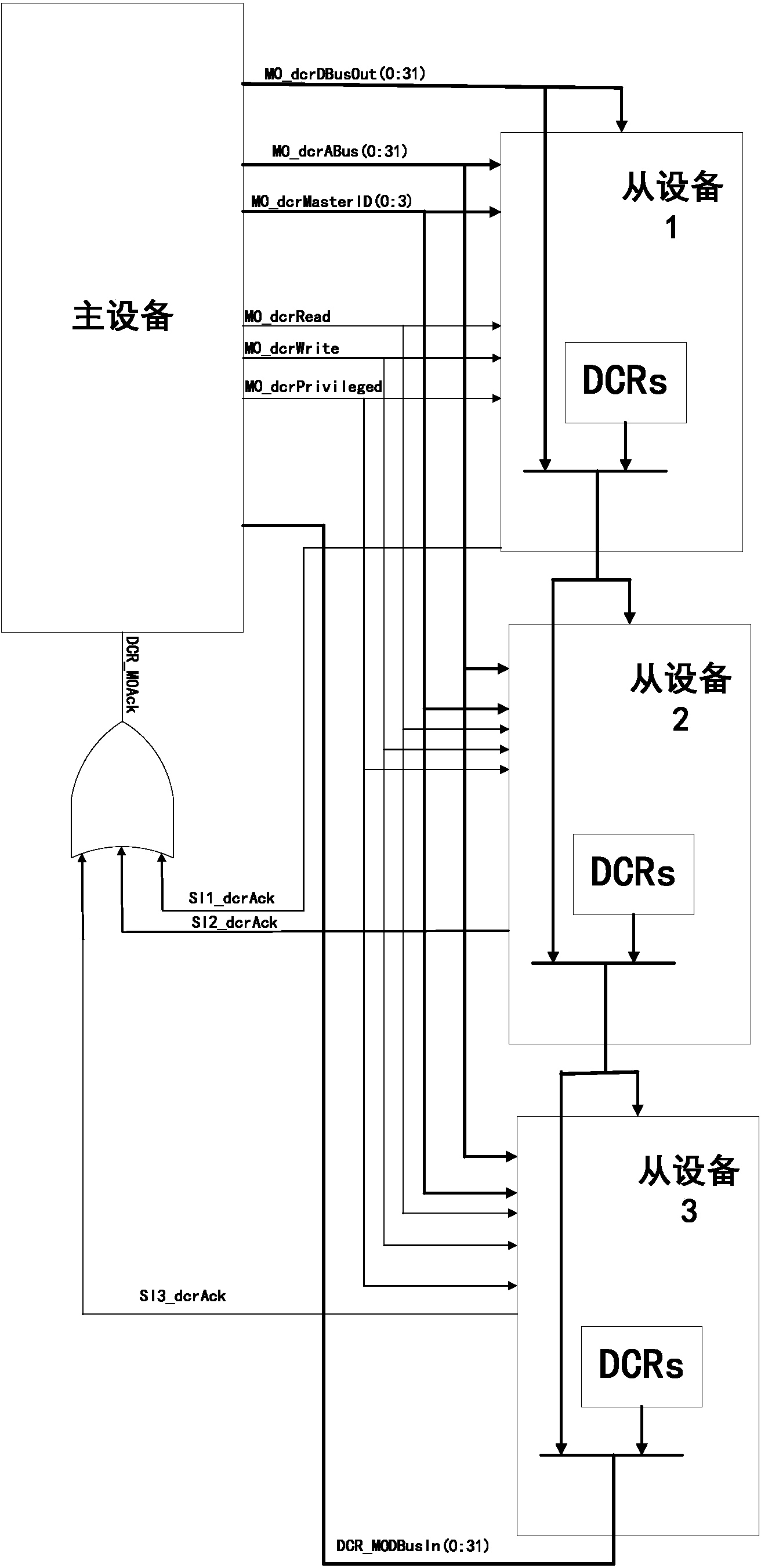

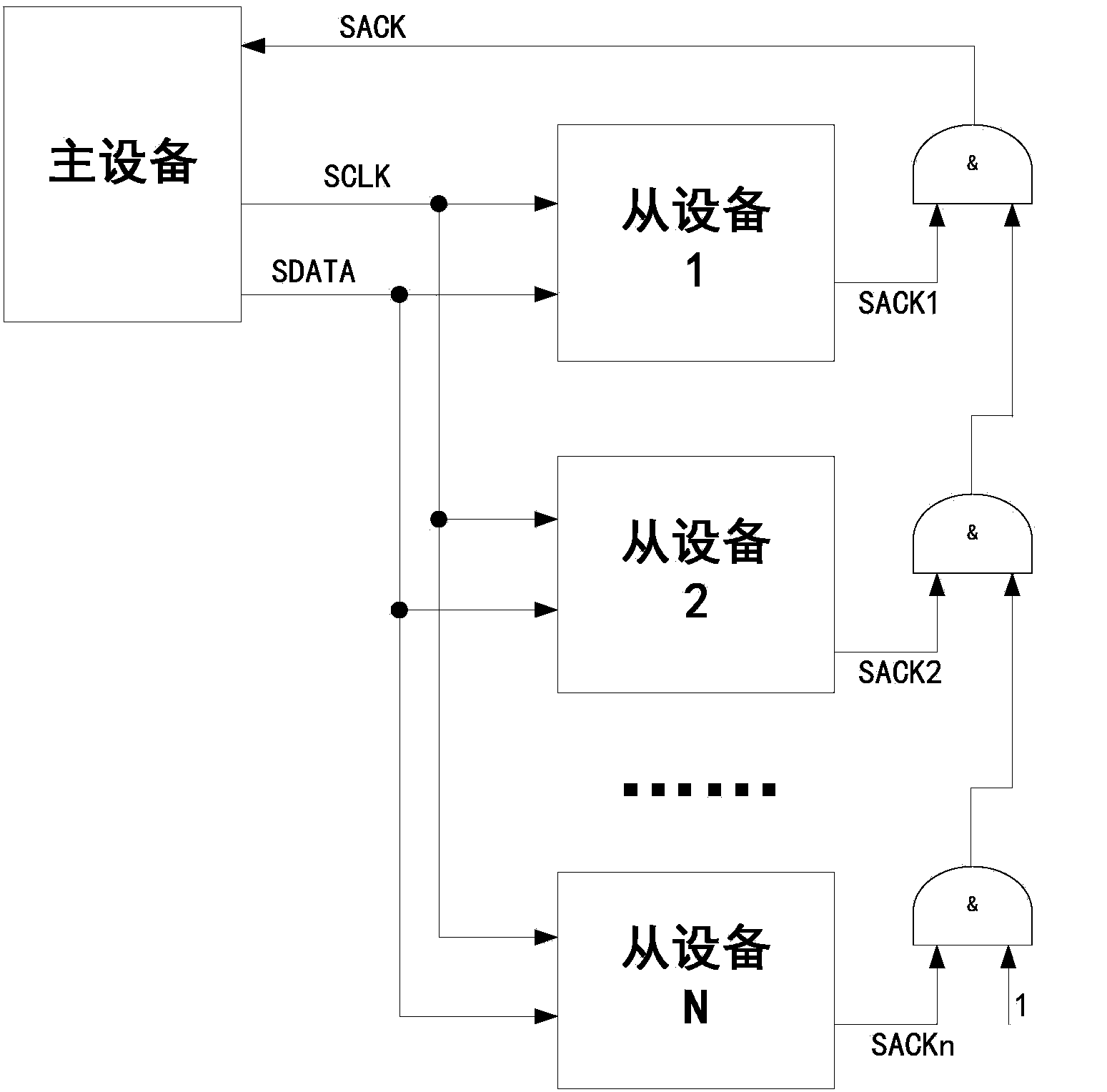

[0030] 1) Connect the clock output interface of the master device to each slave device through a clock line in advance, connect the data interface of the master device to each slave device through a data line, and connect the response lines of each slave device through the After logically cascading, it is finally connected to the response interface of the master device; when the master device sends a message to the slave device, it divides the message into five micro In the micropacket transmission process, each slave device synchronizes with the master device through the clock line of the master device, and the timing of each slave device exchanging data and responding is completely determined by the clock sent by the master device; the master device passes the clock line, data Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com