Cross-platform multilevel integrated design system for FPGA (field programmable gate array)

An integrated design and FPGA technology, applied in the field of microelectronics, can solve the problems of not providing fast design and verification of FPGA, and achieve the effect of shortening the research and development cycle, improving efficiency, and reducing complex operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments, so that those skilled in the art can better understand the present invention and implement it, However, the examples given are not intended to limit the present invention. While illustrations of parameters including particular values may be provided herein, it should be understood that parameters need not be exactly equal to the corresponding values, but rather may approximate the values within acceptable error margins or design constraints.

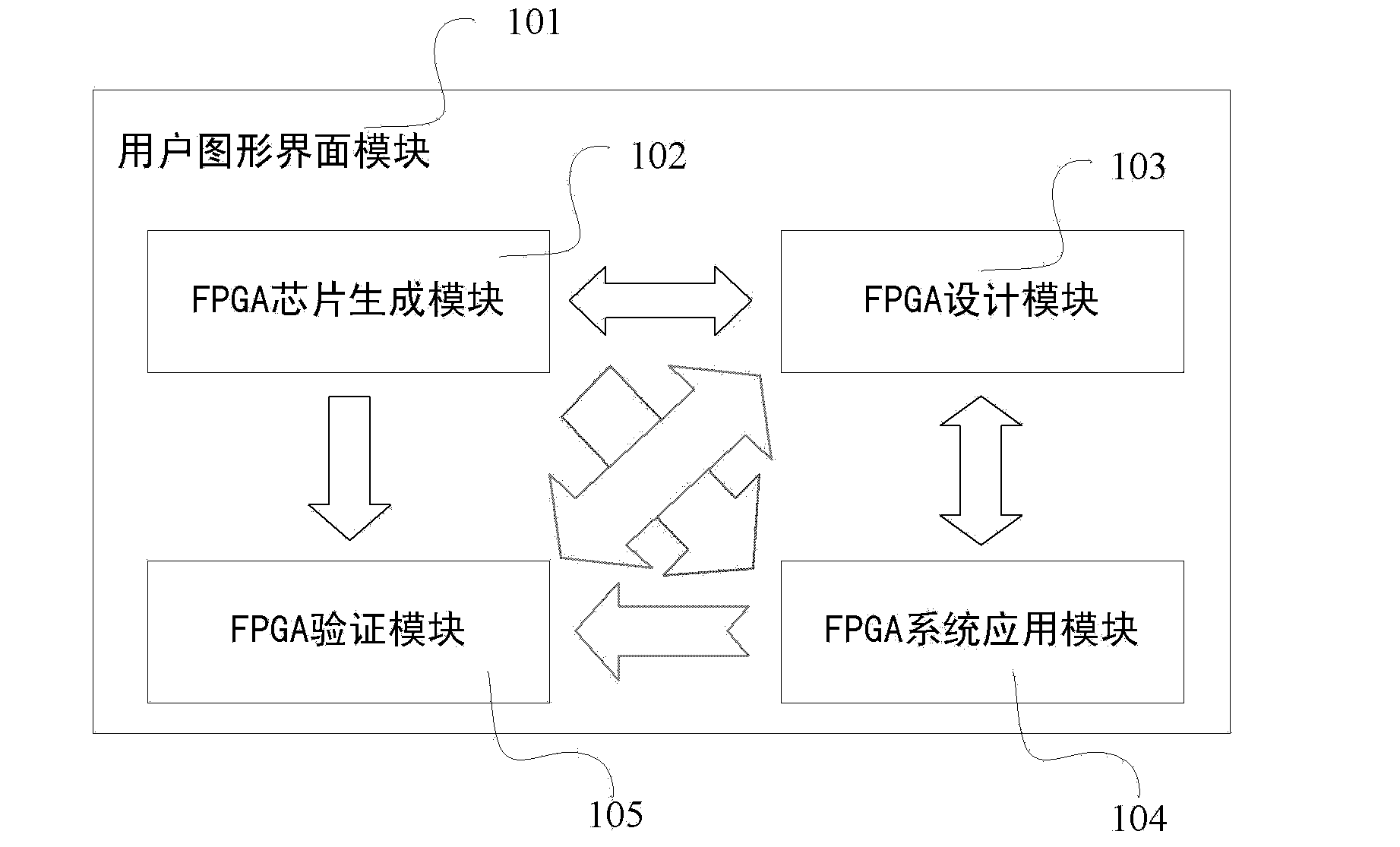

[0041] Such as figure 1 as shown, figure 1 It is a structural block diagram of a multi-level integrated design system for FPGA according to an embodiment of the present invention, and the system includes: graphical user interface module 101, FPGA chip generation module 102, FPGA design module 103...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com