Method for performing high-speed communication by accessing SDRAM (synchronous dynamic random access memory) at different time intervals on basis of FPGA (field programmable gate array) and DSP (digital signal processor)

A high-speed communication, time-based technology, used in instruments, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

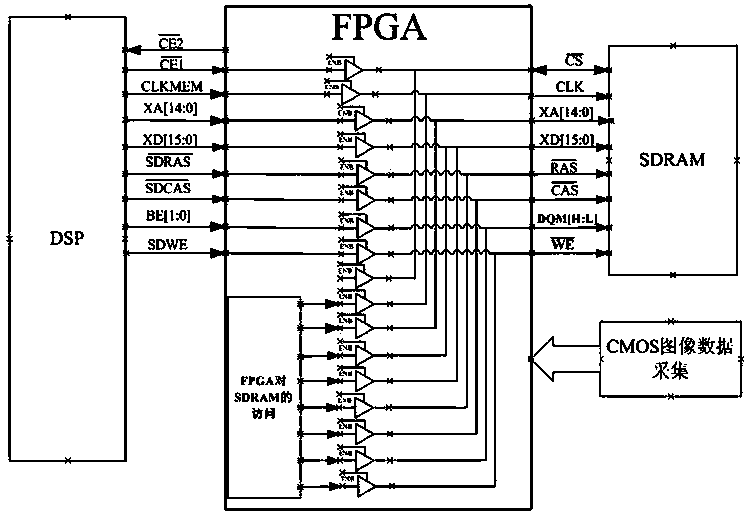

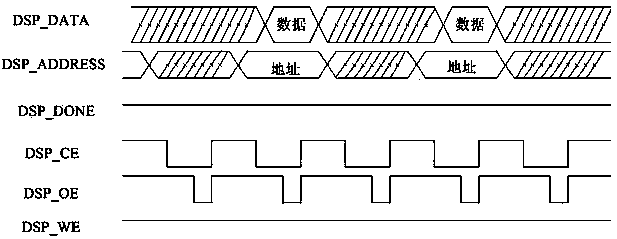

[0022] The method for high-speed communication between FPGA and DSP of the present invention by accessing SDRAM in different periods will be further described below in conjunction with the accompanying drawings and specific implementation methods.

[0023] The present invention is based on the method for FPGA and DSP to access SDRAM by time division for high-speed communication, and the system based on FPGA and DSP to access SDRAM by time division to perform high-speed communication includes FPGA, DSP, communication intermediary memory SDRAM, based on FPGA and DSP through time division access The method for high-speed communication of SDRAM is: the state switching switch in FPGA realizes the two states of FPGA and DSP accessing SDRAM; and the state switching switch in FPGA directly reads data from the communication intermediary memory SDRAM through the communication interface module for processing.

[0024] In the specific implementation method, what FPGA adopts is Cyclone II...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com