Anti-interference A/D (analog-to-digital) chip for Compass satellite navigation

A Beidou satellite and chip technology, applied to satellite radio beacon positioning systems, measuring devices, instruments, etc., can solve the problems of increasing the number of circuit connection pins, power consumption, volume increase, and occupying receiver processors, etc., to achieve The effect of reducing power consumption and PCB layout area, improving precision and accuracy, and reducing the number of pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further described below in conjunction with the accompanying drawings and embodiments, and the present invention includes but not limited to the following embodiments.

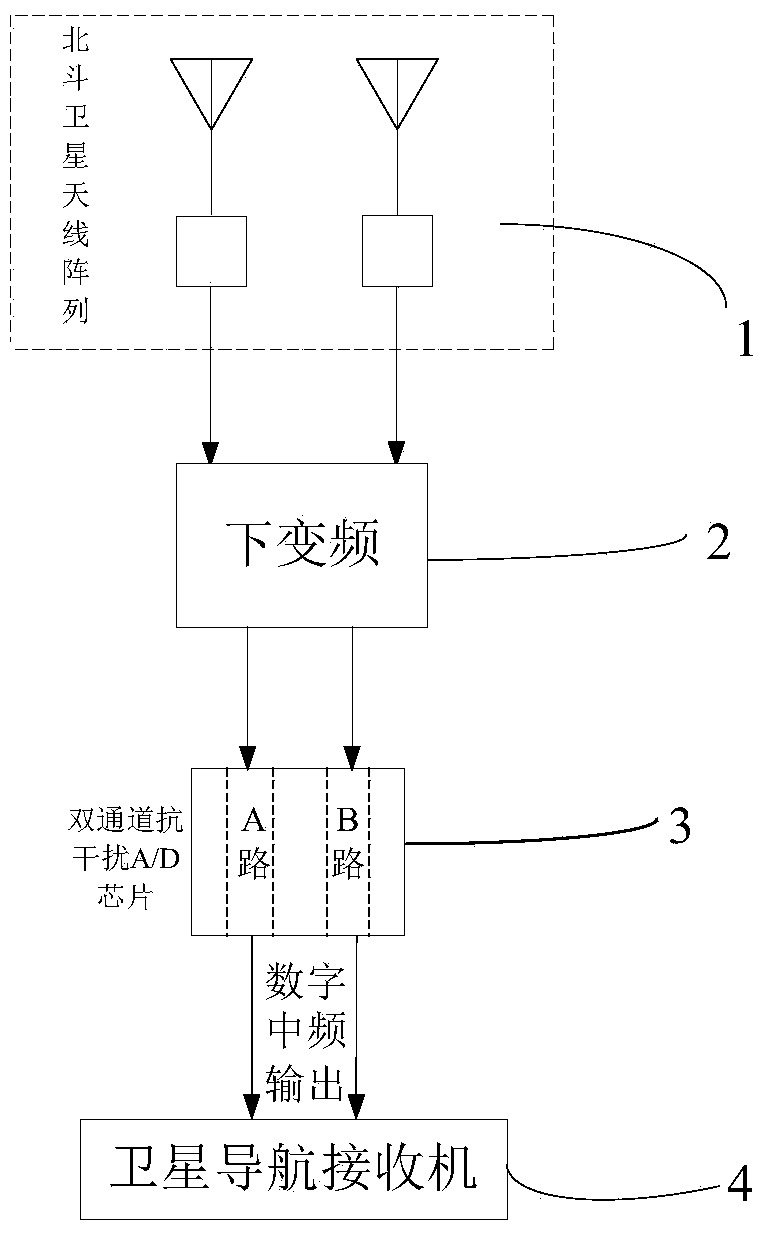

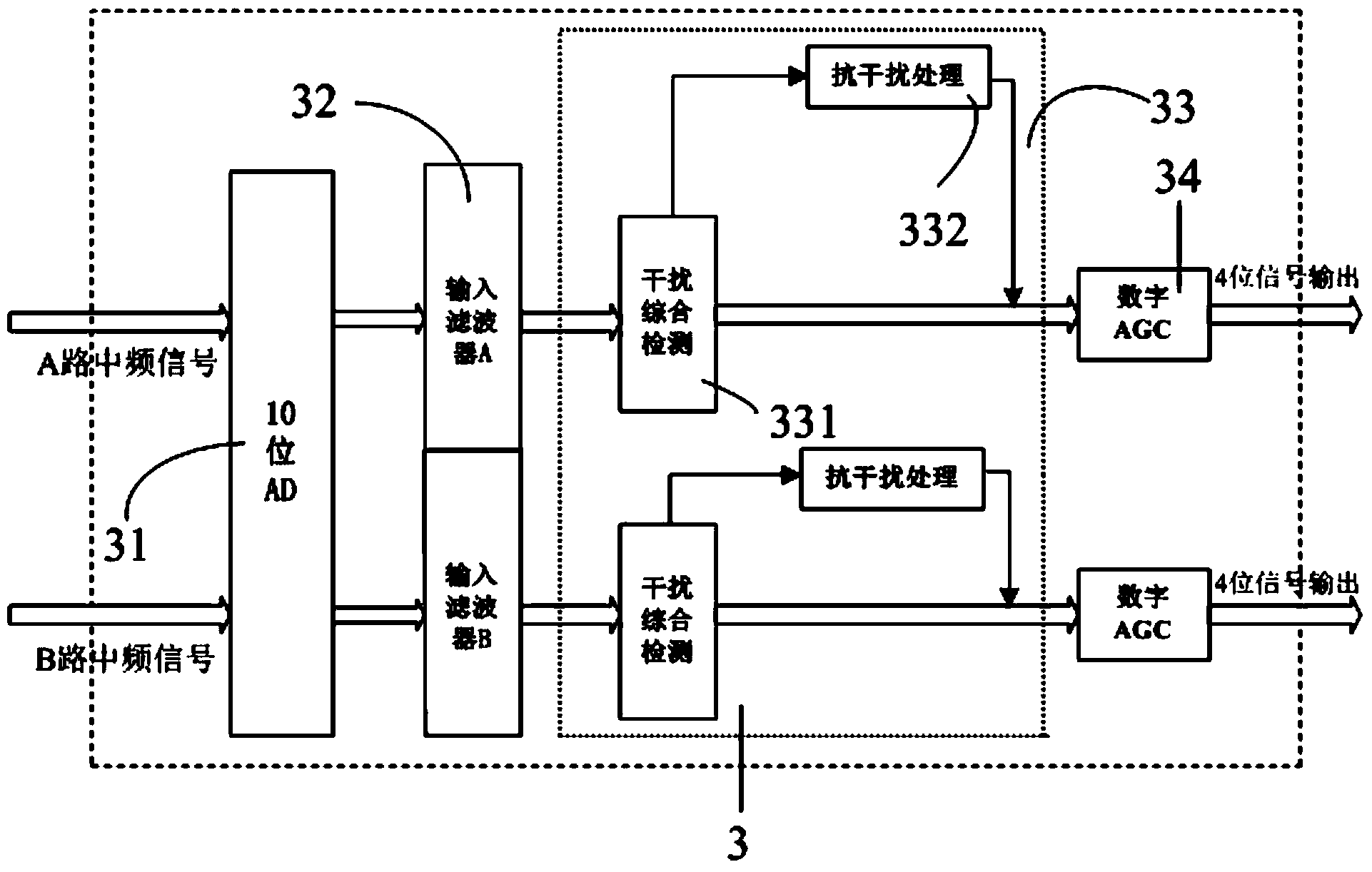

[0016] The satellite navigation anti-jamming A / D chip of the present invention is integrated with two signal channels A and B at the same time, receives two channels of intermediate frequency analog signals, and outputs 4-digit digital signals each. Route A is designed as the signal receiving channel of Beidou 2 B3 frequency point, receiving 46.52MHz intermediate frequency analog signal; Route B is designed as a signal receiving channel of Beidou 1 S frequency point, receiving 12.24MHz intermediate frequency analog signal; Interference type and pin configuration, anti-interference or straight-through processing on the input signal, after the processed signal is stabilized by digital AGC, each channel outputs a 4bit digital signal.

[0017] Such as image 3 As shown, the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com