Structure of stacking chips and method for manufacturing the same

By forming recesses and through-holes on the glass substrate for electrical connection, the problem of complex packaging structures and large area occupation of the image sensor chip and digital signal processor chip is solved, achieving space saving, process simplification and reliability improvement.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

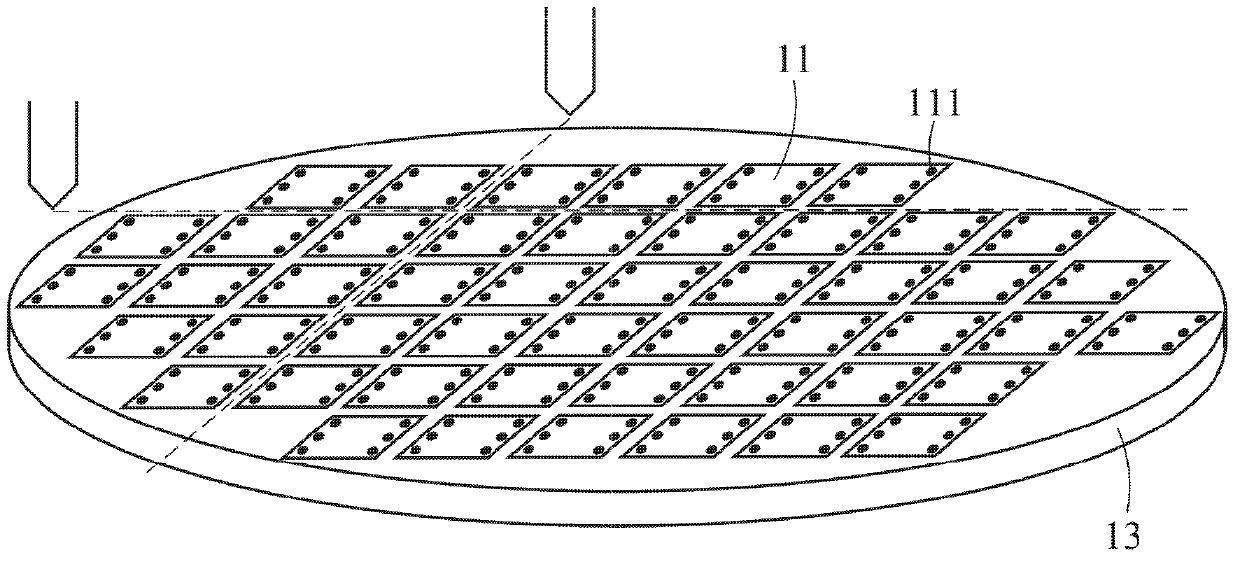

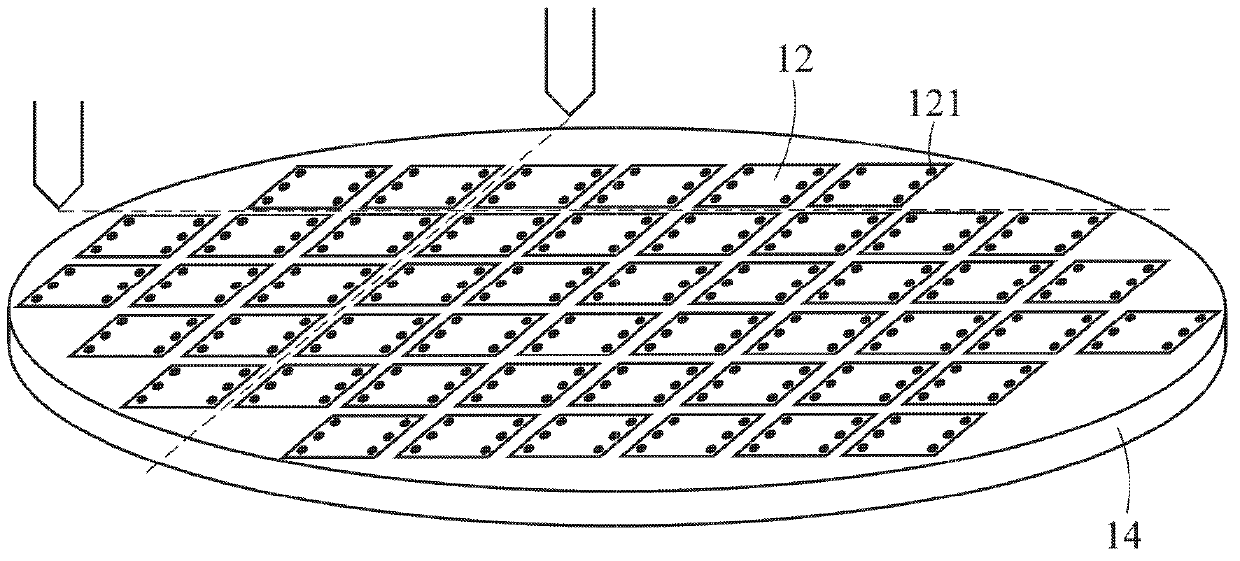

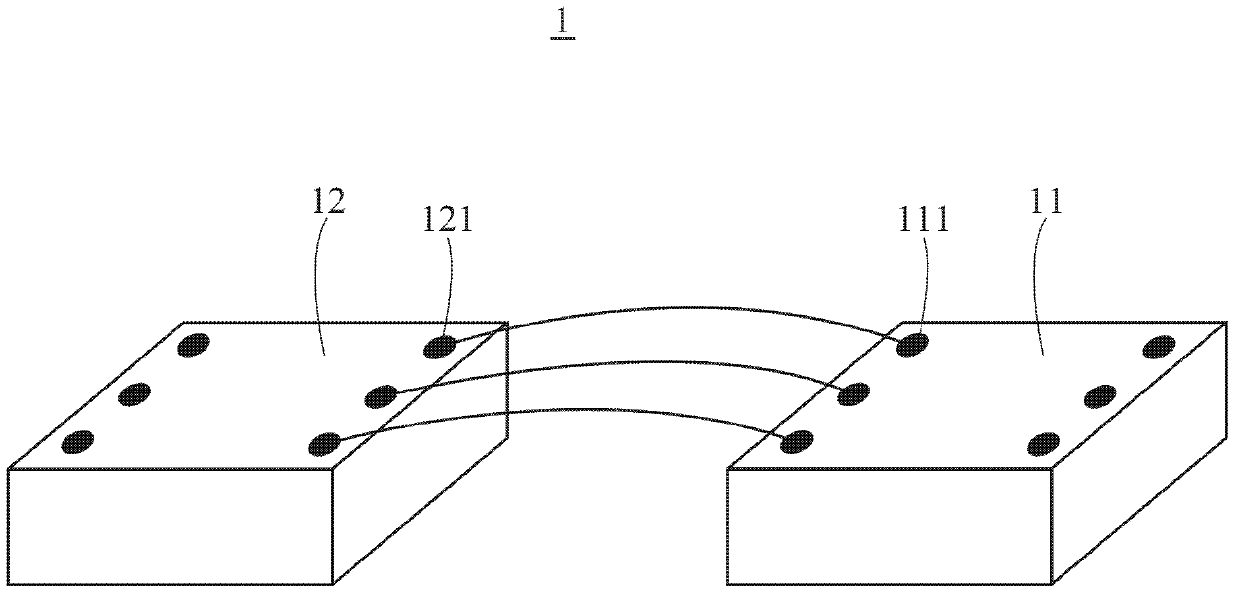

[0044] see figure 2 , is a schematic cross-sectional view of the stacked chip structure 2 according to the first embodiment of the present invention, which is a stacked structure including an optical chip module 21 and a signal processing chip module 23 .

[0045] Wherein, the signal processing chip module 23 includes a glass substrate 231 and a signal processing chip 233 , and the signal processing chip 233 is preferably a digital signal processor (DSP) chip. For the convenience of description, it is further defined that the glass substrate 231 has a first surface 231a and a second surface 231b opposite to the first surface 231a, and the glass substrate 231 is further formed with a plurality of through holes (through holes) 235, in which Metal material is plated to connect the first surface 231a and the second surface 231b.

[0046] A cavity 237 is further formed on the first surface 231 a of the glass substrate 231 for the signal processing chip 233 to be disposed in the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com