A soldering substrate for electronic products and its preparation method

A technology for electronic products and substrates, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of complex process, low solder quantity control accuracy, low chip welding positioning accuracy, etc., to achieve good flatness, high precision, Good welding performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

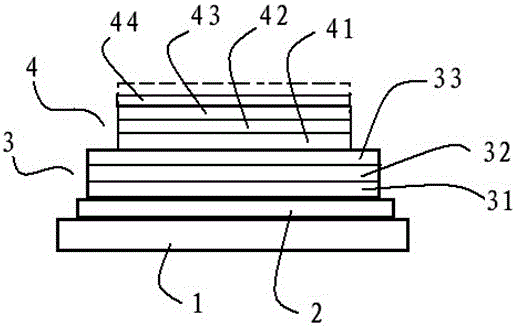

[0022] Such as figure 1 As shown, the electronic product welding substrate of the present invention comprises an alumina ceramic substrate 1, a metallized pattern layer 2 is provided on the substrate 1, and a gold-tin thin film layer 4 is arranged on the metallized pattern layer 2, and the gold-tin The thin film layer 4 is a multilayer structure in which gold layers and tin layers are alternately compounded and the uppermost layer is a gold layer. A barrier layer 3 is provided between the layer 4 and the metallized pattern layer 2. The barrier layer 3 is a three-layer metal layer structure, and the lower layer film 31 is composed of a tungsten-titanium alloy (WTi) layer, and a nickel-platinum-palladium layer. The middle film composed of alloy (NiPtPd) layer, the upper film composed of gold (Au) layer; the thickness of the tungsten-titanium alloy layer is 0.05-0.15µm, the thickness of the nickel-platinum-palladium alloy layer is 0.2-1µm, and the thickness of the gold layer is 0...

Embodiment 2

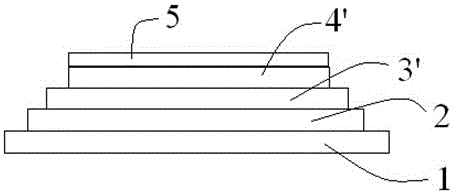

[0041] Such as figure 2 Shown, the welding substrate for electronic product of the present invention comprises alumina ceramic substrate 1, and substrate 1 is provided with metallized pattern layer 2, is provided with gold-tin film layer on this metallized pattern layer 2, and this gold-tin film layer The layer is a gold-tin alloy (AuSn) layer 4' with a thickness of 1.5-5µm; a barrier layer is provided between the AuSn layer 4' and the metallized pattern layer 2, and the barrier layer is a platinum-palladium alloy (PtPd) layer 3', Layer thickness 0.5-1µm. The barrier layer of the present invention prevents the interdiffusion between the gold-tin film and the underlying metallization pattern layer during the soldering process. The gold-tin alloy layer 4' can adopt commonly used gold-tin components 70 / 30, 73 / 27 or 80 / 20; in order to make welding more effective, a gold layer is also provided on the entire area of the gold-tin alloy layer 4' 5. The method described in Exampl...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com