multi-chip package

A multi-chip packaging and chip technology, which is applied to electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of chip and packaging substrate damage, yield decline, cost increase, etc. The effect of transmission delay reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

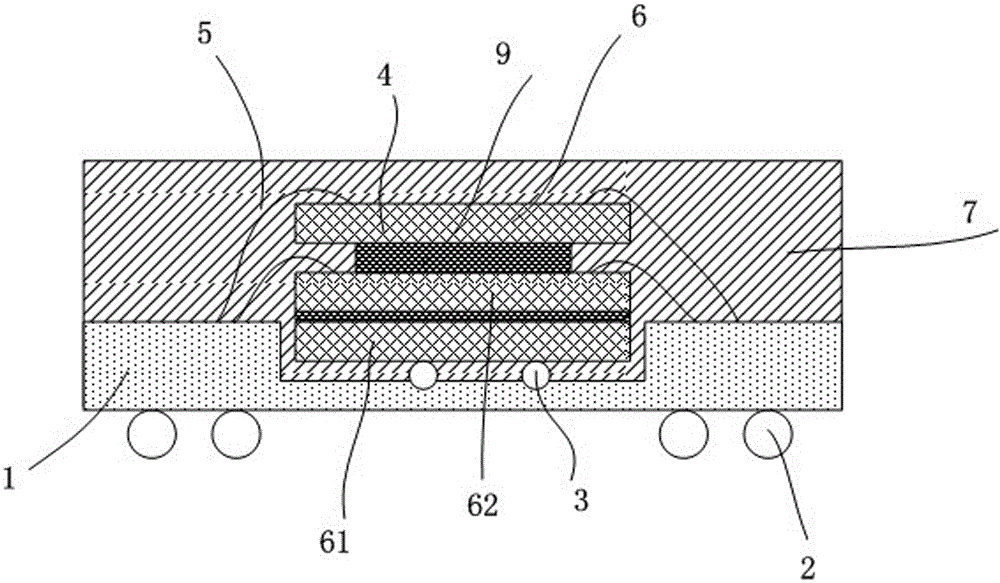

[0027] Generally speaking, semi-open multi-chip packaging technology is commonly seen as figure 1 In the stacked structure shown, a first chip 61 is attached to a groove of a substrate 1 with an upper opening, connected by solder balls 3 or wire bonding, and the second chip 62 is attached to the first chip with the front facing up. On the back side, the second chip 62 is electrically connected to the lead-out end on the upper surface of the substrate 1 by wire bonding, and a blank chip 9 is glued to the middle of the second chip 62, and the third chip 6 is glued on the blank chip 9. The third chip 6 is electrically connected to the corresponding lead-out end on the upper surface of the substrate 1 by wire 5 bonding, and a package body 7 is formed by sealing with resin, and solder balls 2 are planted on the lower surface of the substrate 1 corresponding to the lead-out port of the circuit to form a known A package structure.

[0028] Such as figure 1 The structure shown resul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com