C program to register transfer level (RTL) comprehensive method of pipeline division and module parallel optimization

A synthesis method, c-to-rtl technology, applied in the field of hardware design automation, can solve problems such as unsatisfactory quality of synthesis results, design and optimization without considering C language, inability to express hardware timing, etc., to enhance practicability and applicability range, the effect of improving hardware performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The specific implementation manner of the invention will be further described below in conjunction with the accompanying drawings and embodiments. The following examples are only used to illustrate the present invention, but not to limit the scope of the present invention.

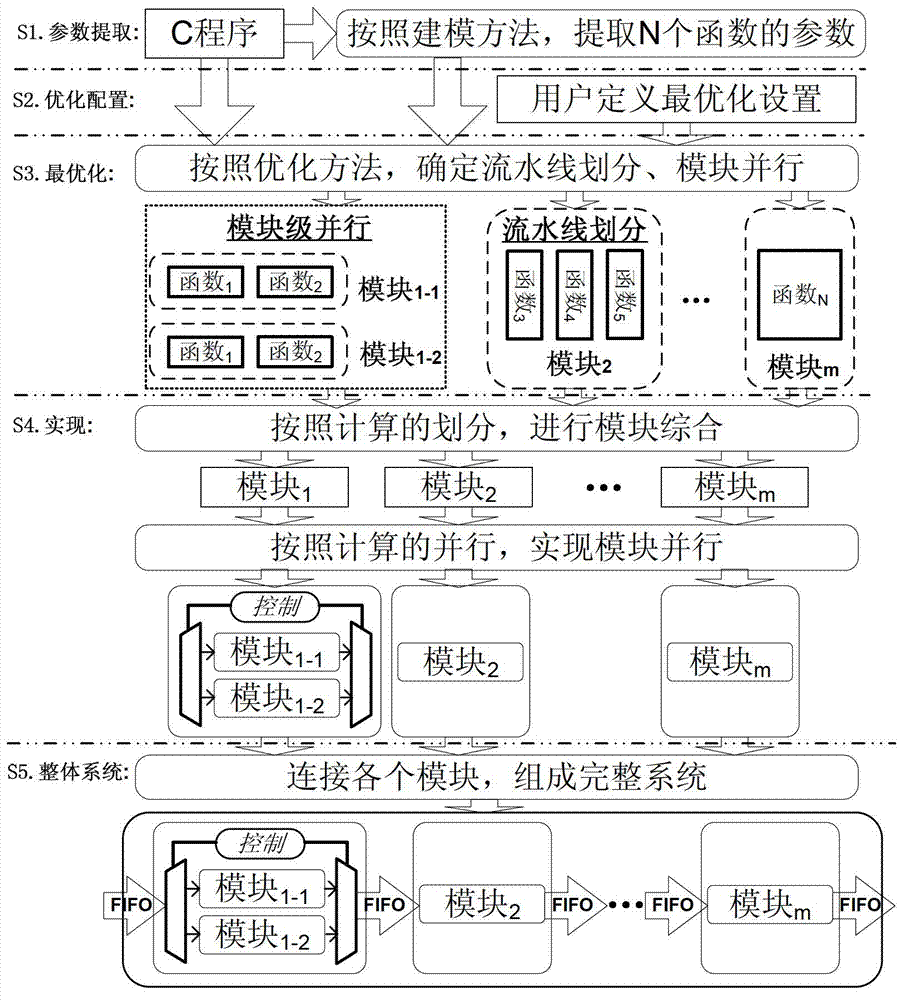

[0041] Flowchart such as figure 1 The shown C-to-RTL synthesis method for pipeline division and module parallel optimization mainly includes the following steps:

[0042] S1. Using the existing C-to-RTL tool, synthesize each function to be synthesized in the input C program in advance, and then extract or calculate the function parameters after synthesis; wherein, the C program is required to be composed of N functions, and these to-be-synthesized functions are required The connection topological relationship of the synthesis function is linear, and this requirement can be realized by modifying the programming style of the C program. Wherein, the function parameters include function operation peri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com