Common image surface imaging method based on CMOS (complementary metal oxide semiconductor) package

An imaging method and imaging technology, which are applied in the directions of image communication, color TV parts, TV system parts, etc., can solve the problem of increasing system complexity, poor imaging effect at the junction between image planes, and inability to realize system miniaturization design. requirements, etc., to avoid the poor junction of the imaging area and avoid the effect of the image effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the purpose, technical solution and advantages of the present invention clearer, the implementation manners of the present invention will be further described in detail below.

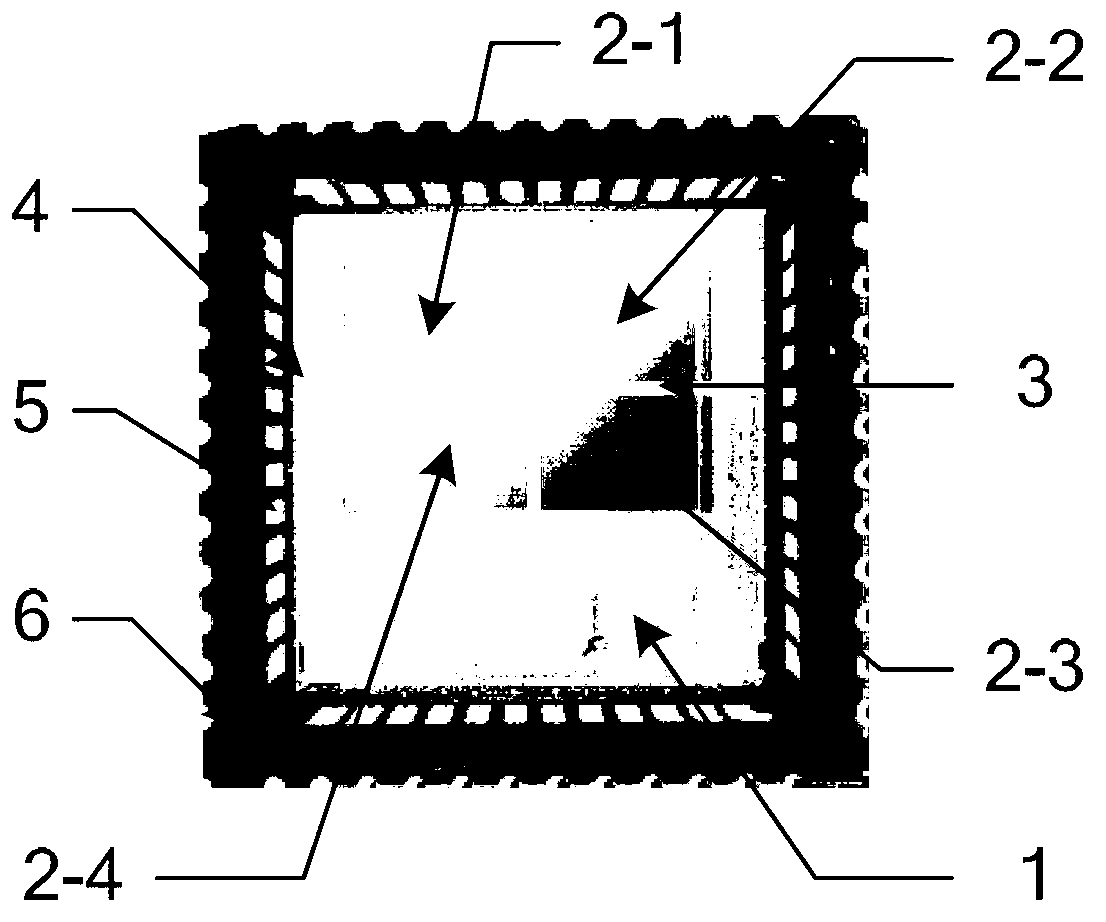

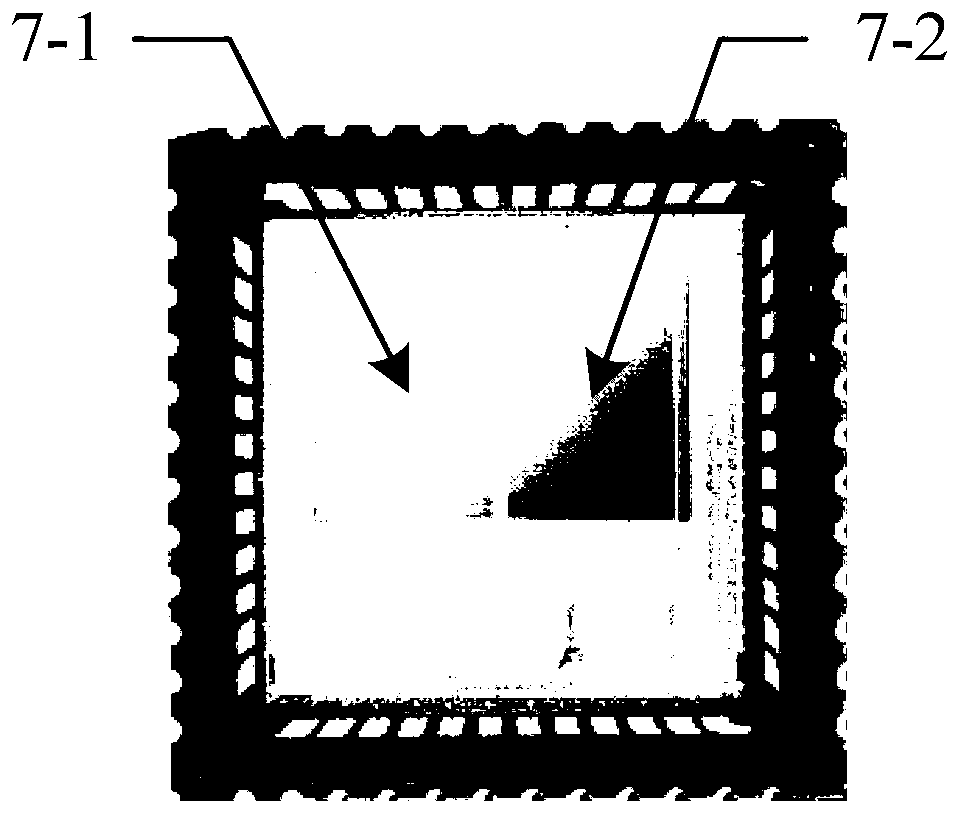

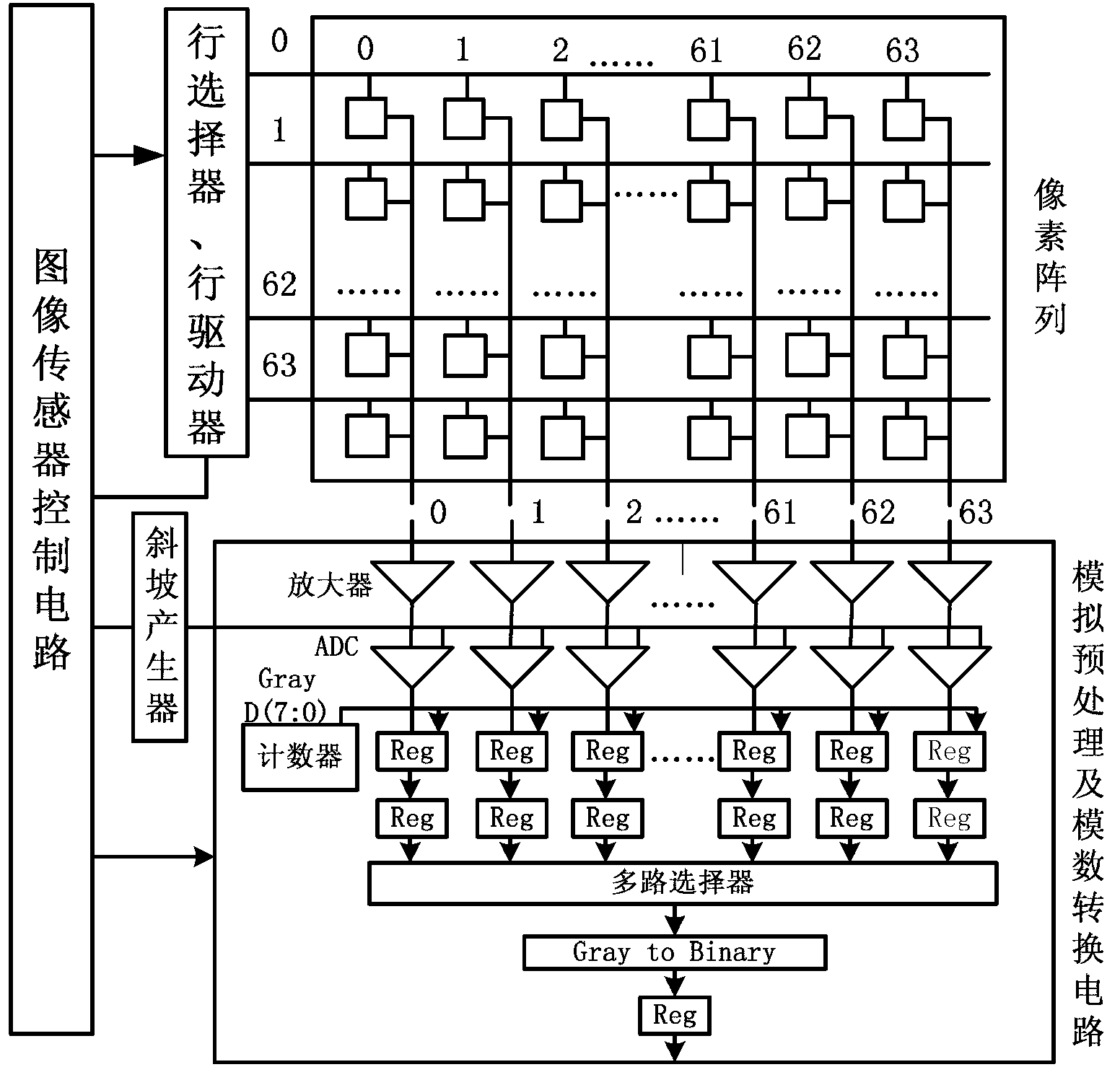

[0027] see figure 1 and Figure 4 , in order to meet the requirements for real-time detection applications and system miniaturization design, and improve the imaging effect at the junction of the segmented image planes, an embodiment of the present invention provides a common image plane imaging method based on CMOS packaging, see the following description for details:

[0028] 101: Carry out partitioned imaging layout on the imaging sensing area of the photosensitive chip 1, divide it into at least two imaging sensing areas 2, adjacent imaging sensing areas 2 are separated from each other by a spacer area 3, and each imaging sensing area 2 corresponds to an optical sensing area 2 Channels, different scene information or different spectral information of the same scene are si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com