Microprocessor instruction set validation method

A microprocessor and verification method technology, applied in the direction of digital data authentication, multi-program device, etc., can solve the problems that the verification code cannot be completely covered, lack of verification incentives, etc., and achieve the effect of high-efficiency verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

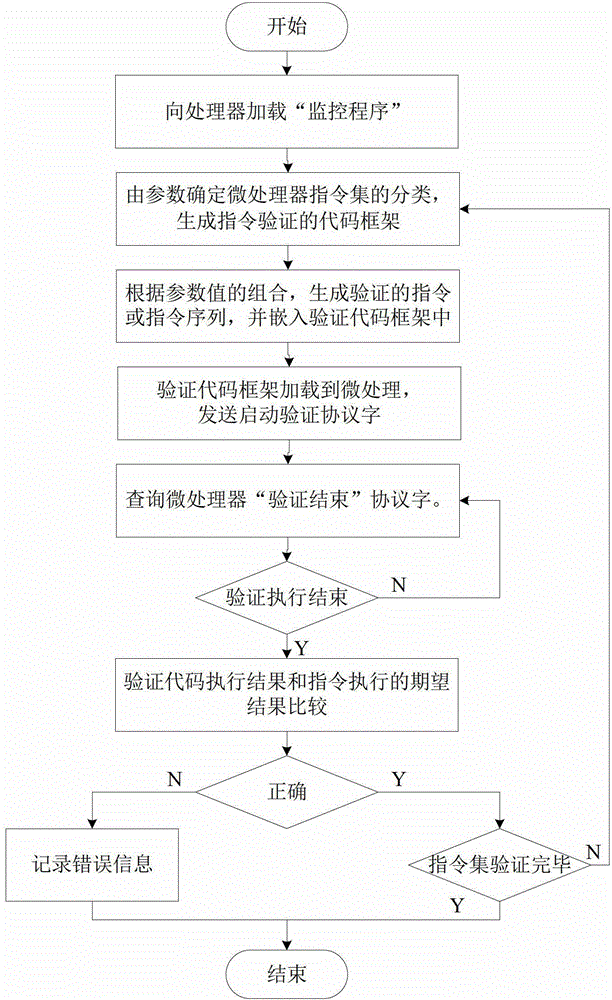

[0029] The present invention comprises the following steps:

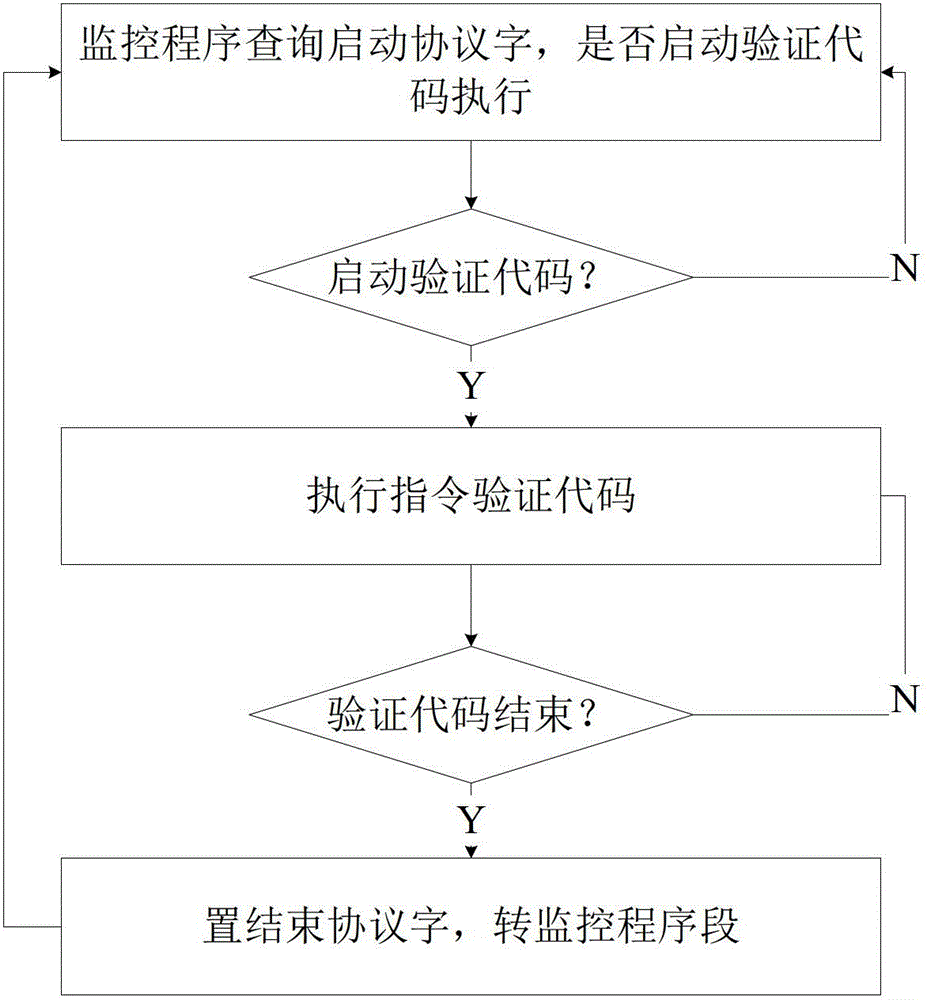

[0030] Step 1, the monitoring program is loaded into the microprocessor, and the microprocessor is started to run the monitoring program;

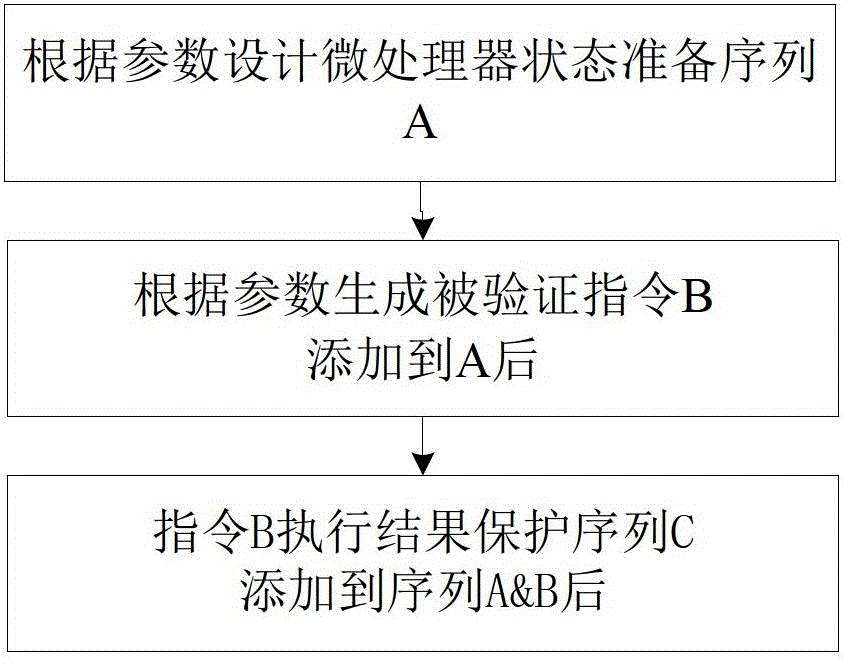

[0031] Step 2. Classify the instruction sets supported by the microprocessor, and each type of instruction is determined by a set of parameters. For each type of instruction, design a code framework for instruction verification, and the instructions or instruction sequences that need to be verified are embedded in this code framework;

[0032] Step 3. Traversing the values for each group of parameters according to the fetching range, generating a verified instruction or instruction sequence according to the combination of each group of parameter values, and embedding the instruction or instruction sequence into the verification code framework of step 2;

[0033] Step 4, load the verification code framework into the microprocessor, and send the protocol word to the monitoring ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com