Electronic devices and systems, and methods for making and using the same

A conductive, nano-scale technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve complex problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

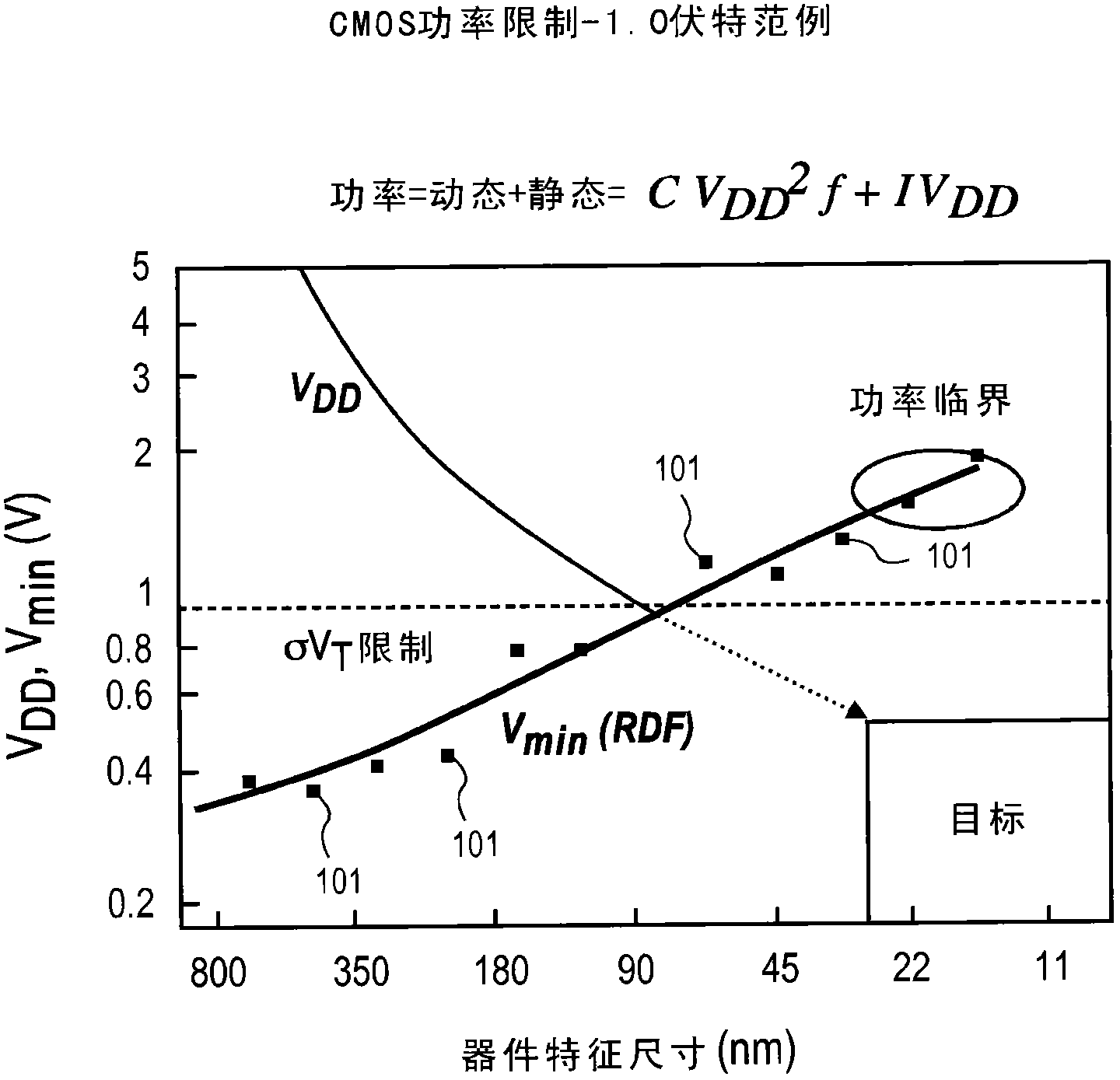

[0085] A novel set of structures and methods are provided to reduce power consumption in large arrays of electronic devices and systems. Some of these structures and methods can be implemented in large numbers by reusing existing bulk CMOS process flows and fabrication techniques, allowing the semiconductor industry, and the electronics industry more broadly, to avoid costly and risky switches to alternative technologies.

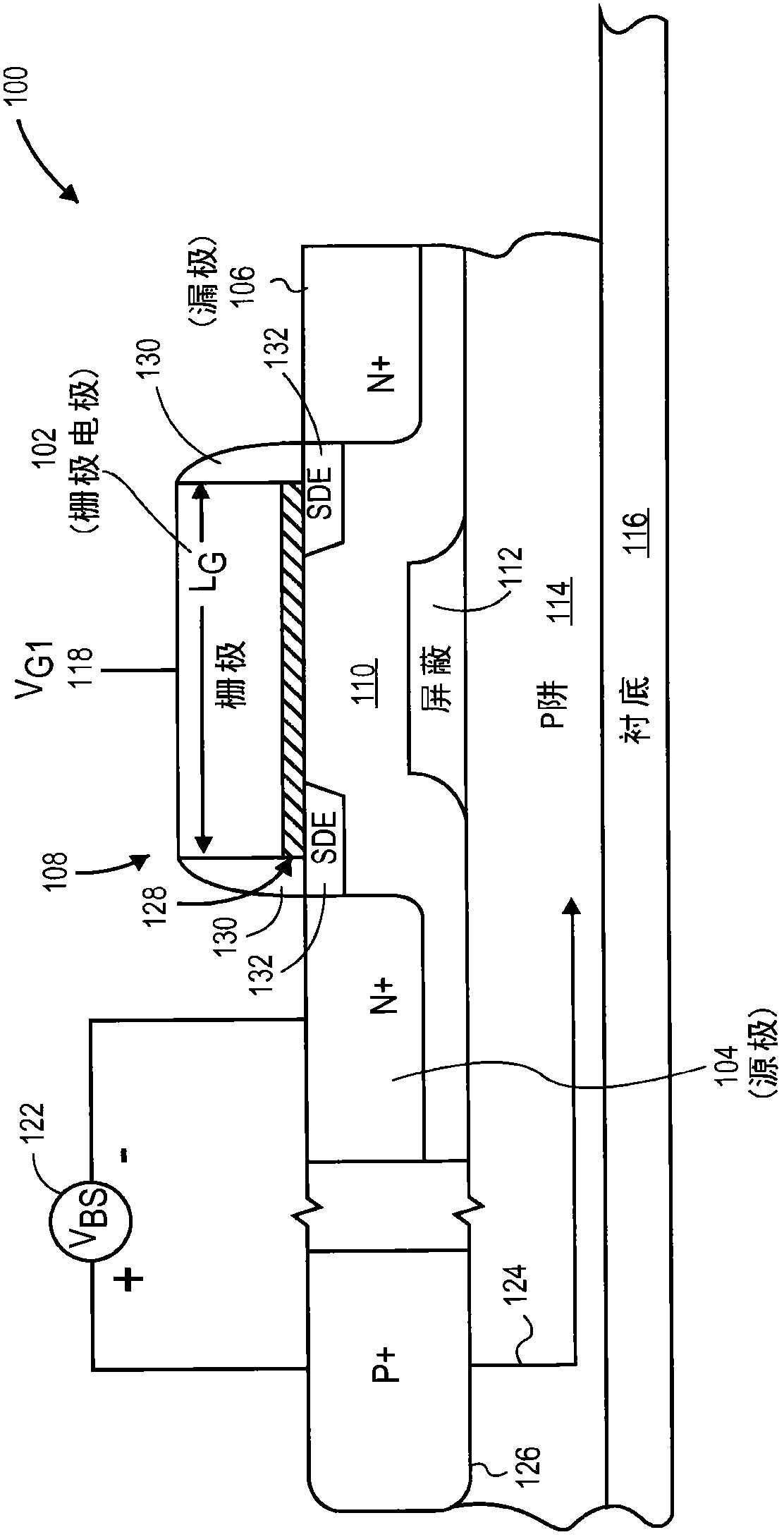

[0086]As noted above, some structures and methods involve deep depletion channel (DDC) designs. DDC can allow CMOS devices with reduced σV compared to traditional bulk CMOS T , and can allow the threshold voltage V of the FET with dopants in the channel region T is set much more precisely. DDC designs can also have a stronger body effect than conventional bulk CMOS transistors, which can allow significant dynamic control of power dissipation in DDC transistors. There are many ways to structure a DDC to achieve different advantages, and the additional fea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com