System and method for verifying register transfer level (RTL) hardware

A register-transfer-level, hardware-implemented technology, applied in the detection of faulty computer hardware, function inspection, etc., can solve the problems of not being able to obtain functional coverage and spending a lot of test time, and achieve the goal of improving efficiency, correctness, and efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

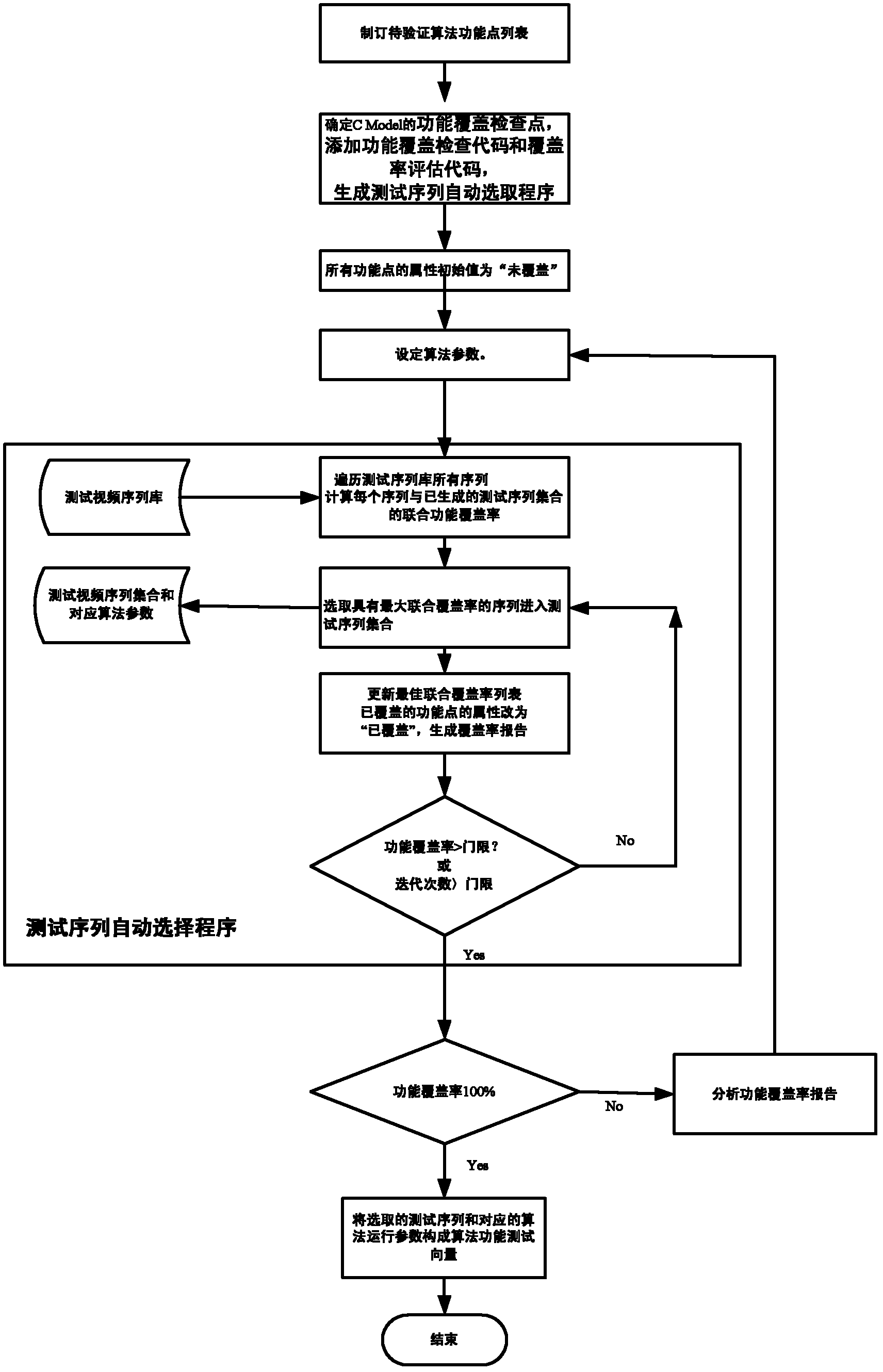

[0024] Usually, the process of verifying the RTL hardware implementation of the video algorithm based on the functional coverage rate is as follows: build a test scene, generate an input stimulus → RTL simulation → coverage analysis, if the coverage rate does not reach the target, repeat the above steps in sequence. When the hardware scale is getting larger and larger, RTL simulation takes a lot of time, so it takes a lot of time to complete one iteration, and multiple iterations are needed to achieve the coverage target, so the overall verification time is huge.

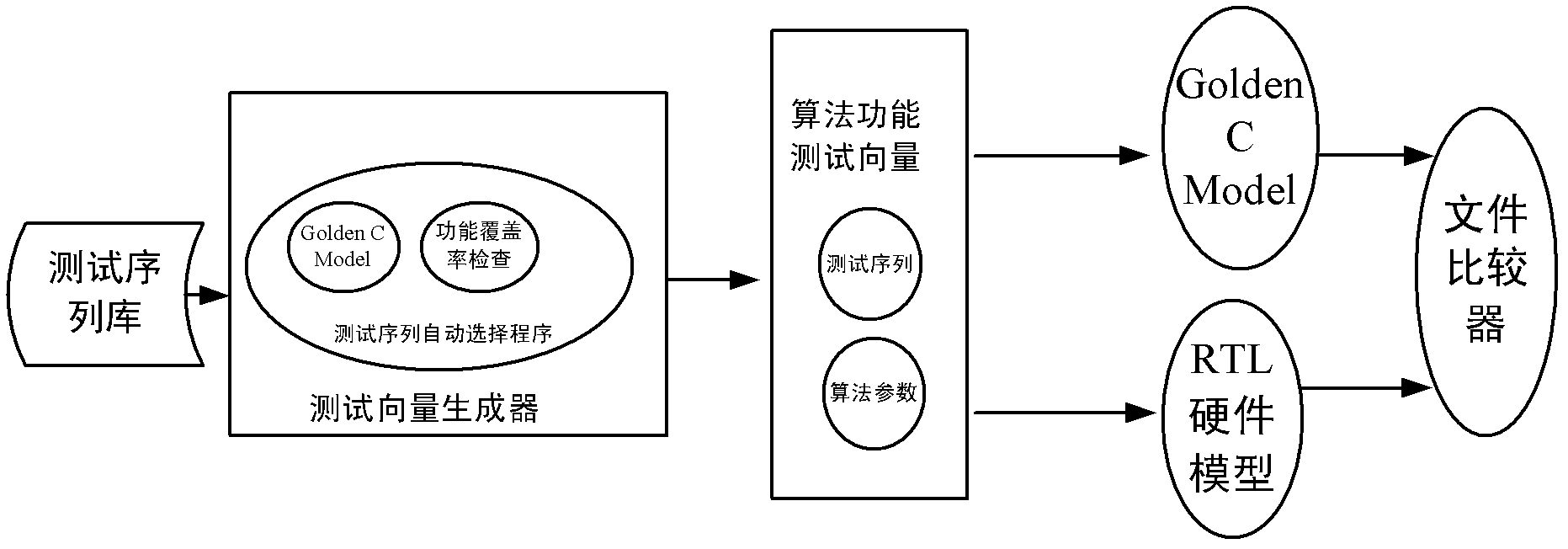

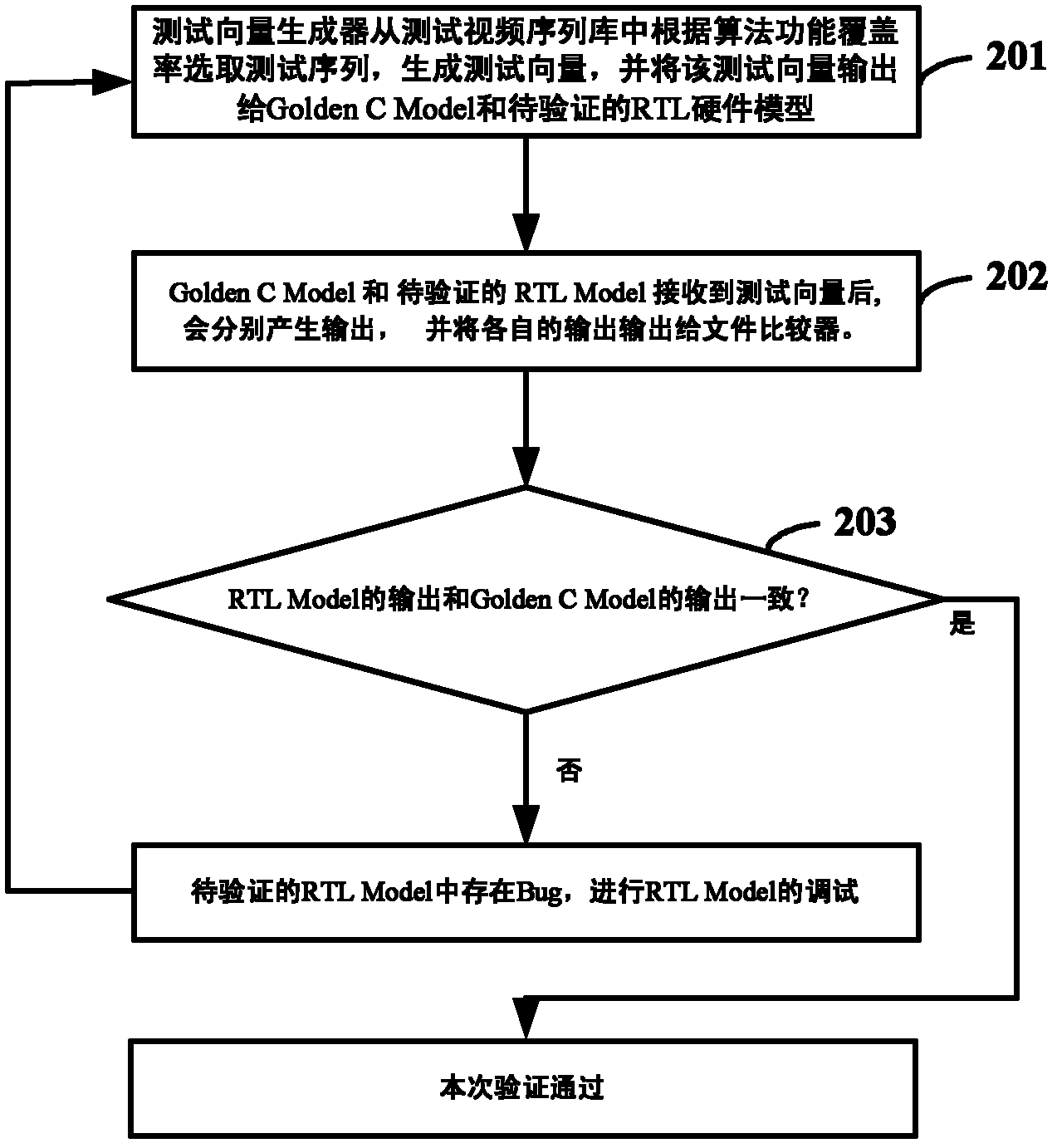

[0025] Aiming at the characteristics of the RTL hardware implementation of the video algorithm, the present invention proposes a system and method for verifying...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com