Cache memory system

A memory system and cache technology, applied in memory systems, instruments, memory architecture access/allocation, etc., which can solve the problems of data write-back soft errors and complicated control of write-back systems.

- Summary

- Abstract

- Description

- Claims

- Application Information

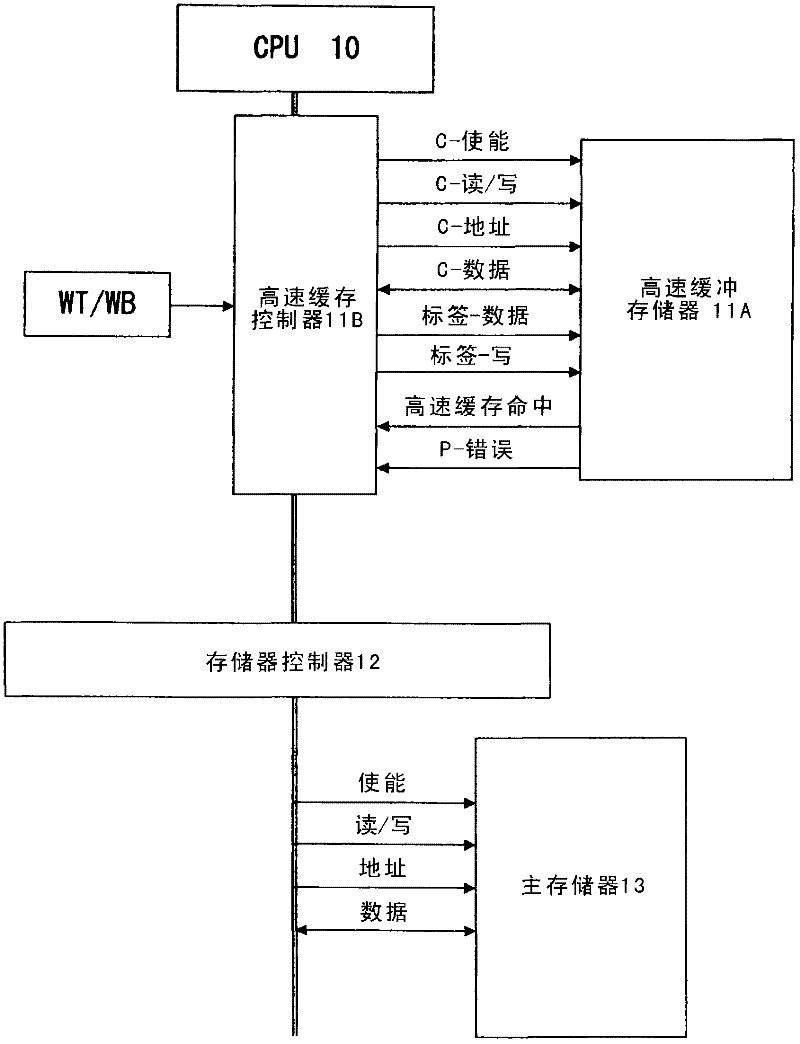

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In this embodiment, the cache memory operates in a write-through system, and the operation performed when a cache miss (mishit) occurs when there is no corresponding data in the cache memory or when there is data but an error occurs be executed. Subsequently, a bit is provided in the cache memory indicating that a soft error has previously occurred. If an error occurs again when this bit indicates "1", it is judged that a hardware error has occurred, and an interrupt is generated in the CPU. Judgment as to whether or not a hardware error has occurred is performed by providing a register that is set when an error occurs in the cache memory and is reset at intervals sufficiently shorter than the frequency at which soft errors occur. If an error occurs in the cache memory when this register is set, it is judged that a hardware error has occurred, and an interrupt is generated in the CPU.

[0032] As described above, when there is an error in the data in the cache memory,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com