Method for testing dual inline memory modules (DIMM)

A chip and logic interface technology, applied in the testing field of testing efficiency, can solve the problems of slow testing speed of special testing software, limited number of DIMM slots, high price of server motherboards, etc. fast effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

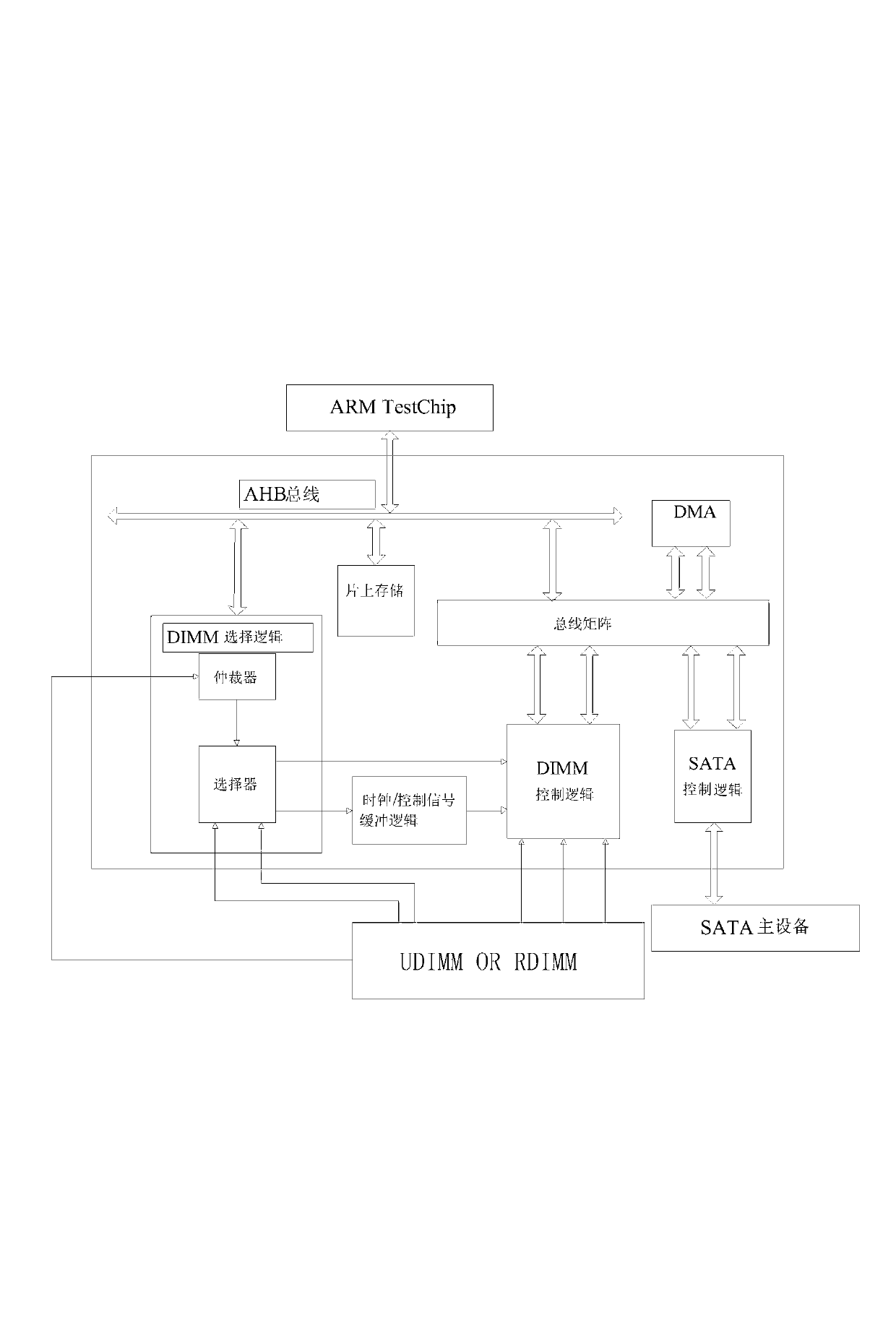

[0017] A method for implementing DIMM testing provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

[0018] In order to improve the efficiency of DIMM testing, realize high-speed reading and writing. as attached figure 1 As shown, a method for implementing DIMM testing is now provided, and its specific implementation steps are:

[0019] First, the field programmable gate array FPGA chip is connected to the control chip, high-speed interface and DIMM logic interface of multiple channels, and the DIMM verification system is composed of FPGA chip, control chip, high-speed interface and DIMM logic interface. The verification system forms an electronic disk; then sends the read and write instructions of the master device to the system through the high-speed interface; finally, the control chip is responsible for the instruction analysis and reads and writes the DIMM to be tested by controlling the DIMM logic to realize ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com