High-level synthesis method and system

A high-level synthesis, compatible graph technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as the inability to meet area design requirements, and achieve the effect of reducing interconnection overhead and rapid generation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

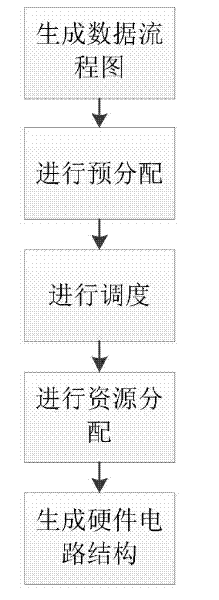

[0048] Depend on figure 1 and figure 2 As can be seen, a high-level synthesis method, the method steps include:

[0049] A. Obtain a description of the behavior of the digital circuit, and then generate a data flow diagram;

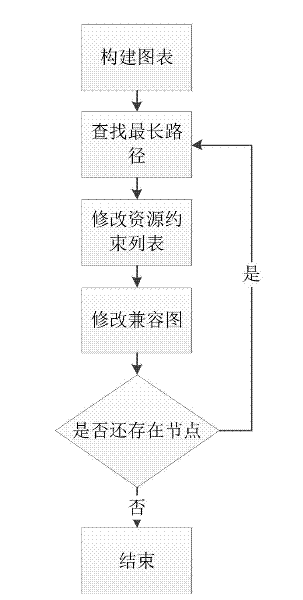

[0050] B. Pre-allocate hardware resources according to the data flow diagram, and then generate a resource constraint list;

[0051] C. Scheduling according to the resource constraint list and data flow graph;

[0052] D. Resource allocation is performed according to the scheduling results;

[0053] E. Generate a hardware circuit structure according to the resource allocation result and the scheduling result.

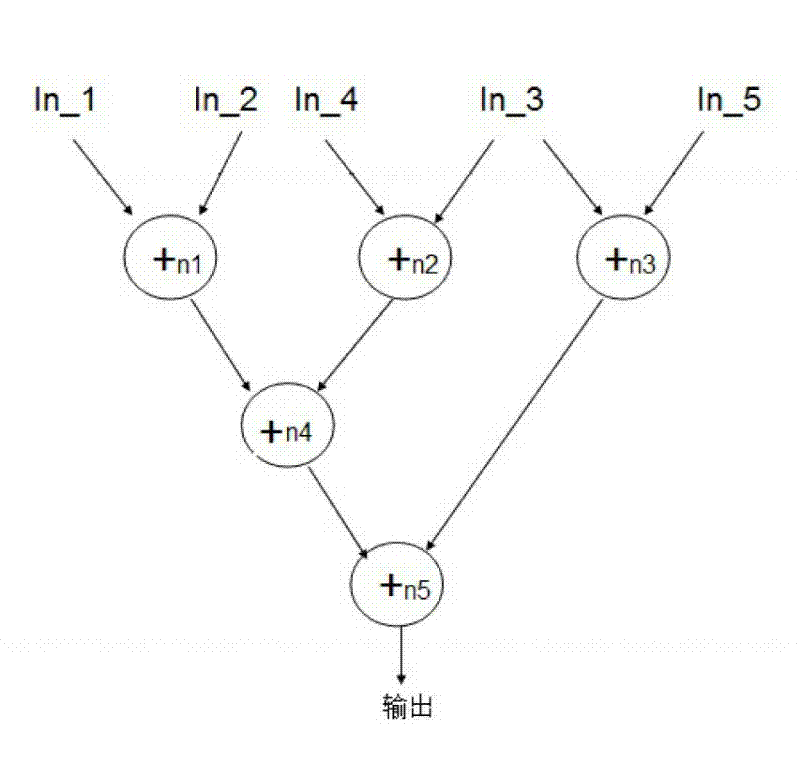

[0054] The above data flow diagram is as follows image 3 As shown, the nodes in the figure represent different types of operations, and the arrows represent the direction of data flow, that is, the data dependencies between operations; the scheduling is the process of allocating operations to each control step, and the resource allocation is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com