Method for realizing cache coherence protocol of chip multiprocessor (CMP) system

A multi-core processor and processor system technology, applied in the field of cache coherence protocol implementation, can solve problems such as inability to complete write operations, and achieve the effects of avoiding starvation, improving performance, reducing power consumption and bandwidth usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

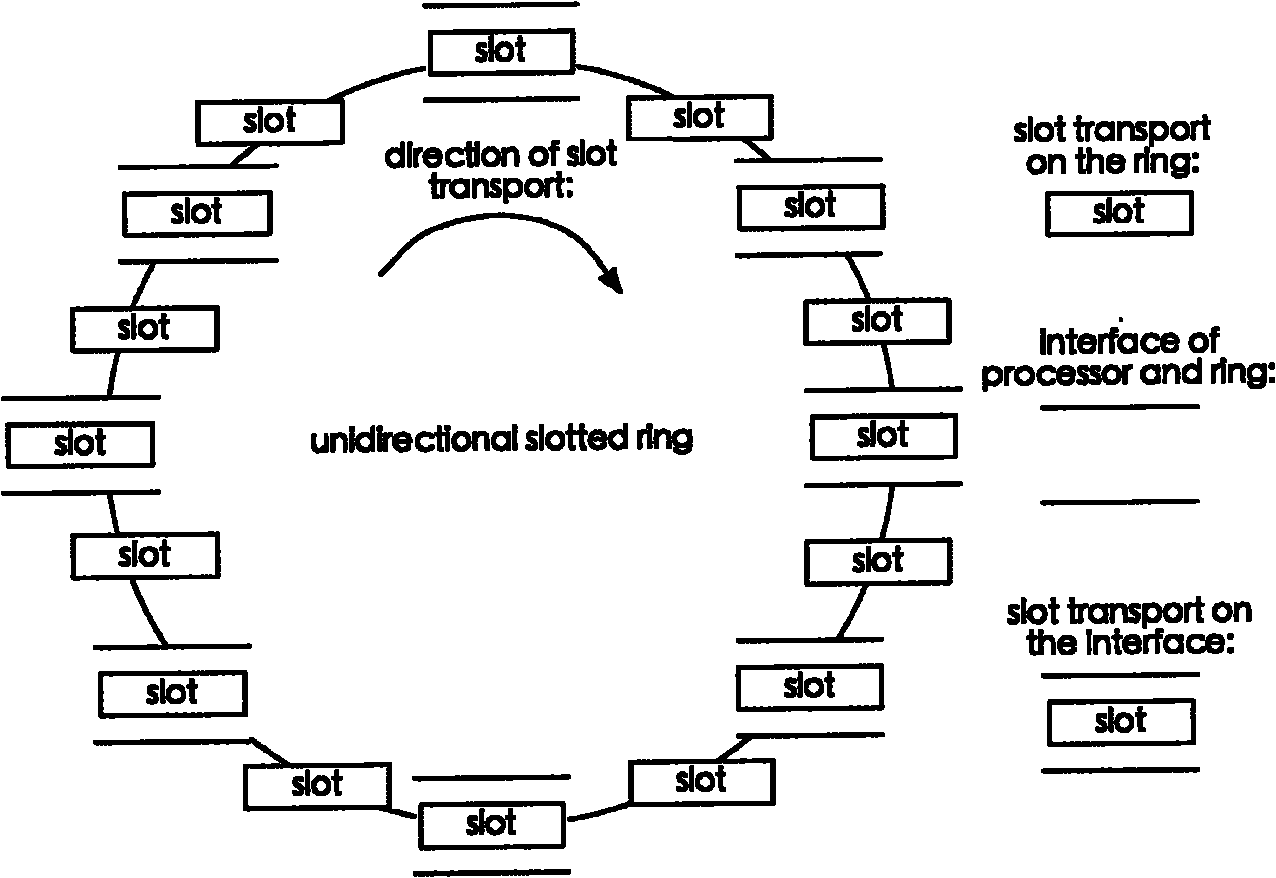

[0060] Such as Figure 7 As shown, it is a structure diagram of eight processor cores with one-way slotted ring connection CMP. This structure is a one-way slotted ring connected to the on-chip multi-core processor structure used in the implementation of the protocol. Figure 7 In , the CMP composed of 8 processor cores is taken as an example to illustrate the structure, P1 to P8 represent 8 processors, and the Cache is divided into two levels of structure, namely the first-level Cache (L1) and the second-level Cache (L2). L1 is divided into instruction cache (L1I) and data cache (L1D), which are private to each processor. L2 is physically distributed among all processors and logically shared by each processor. The one-way slotted ring includes a request information ring and a data informat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com