Implementation method of adaptive clock holdover mode and device thereof

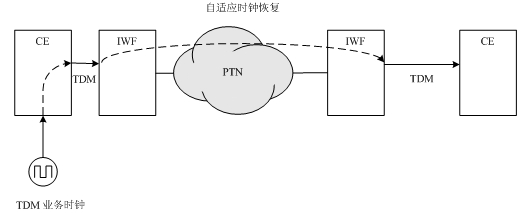

A technology of hold mode and implementation method, applied in time division multiplexing systems, digital transmission systems, data exchange networks, etc., can solve problems such as false triggering of adaptive clock hold mode, and achieve the effect of solving the problem of false triggering

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

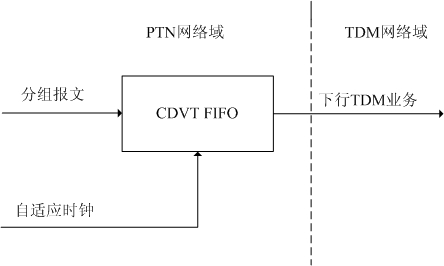

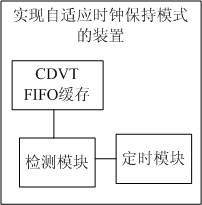

[0027] Can cause the CDVT FIFO to underflow. In addition to network interruptions, the adaptive clock has not yet locked the source clock and is faster than the source clock. It may also cause the CDVT FIFO to underflow. Underflow in this case should not trigger the adaptive clock to enter hold mode , instead keep the adaptive clock in tracking mode to lock to the source clock as soon as possible. Currently, the CDVT FIFO underflow event is commonly used in the industry to trigger the adaptive clock to enter the hold mode. The disadvantage is that it does not distinguish whether the underflow event is caused by a network interruption or because the adaptive clock has not yet locked the source clock. The basic idea of the present invention is to further judge whether the root cause of the underflow is network interruption or the adaptive clock has not locked the source clock after detecting the CDVT FIFO underflow event, and decide whether to trigger the adaptive clock to ente...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com