Full-flow 128-bit-accuracy floating-point accumulator based on full expansion

An accumulator and floating-point technology, which is applied to calculations using the number system and calculations using non-contact manufacturing equipment, and can solve problems such as undiscovered floating-point accumulators

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

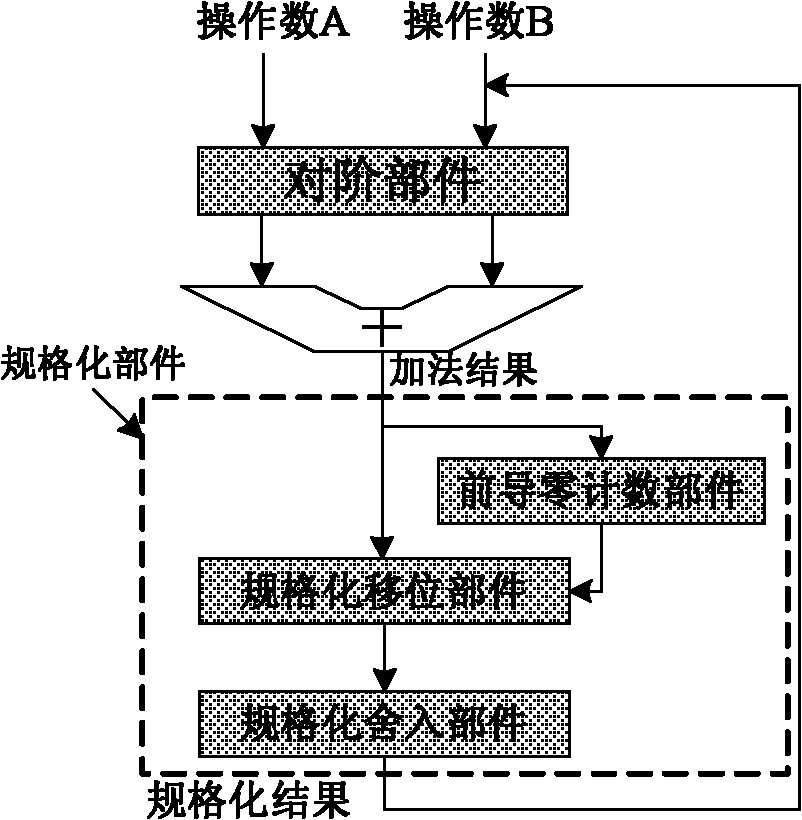

[0053] figure 1 is a general block diagram of an existing accumulator. The existing floating-point accumulator is designed according to the idea of cyclically performing floating-point addition operations, and is mainly composed of an order unit, an adder and a normalization unit. The normalization section consists of a leading zero count section, a normalization shift section, and a normalization rounding section. The pair-order component receives operand A and operand B input from the outside, and shifts the mantissa of the operand with a small exponent to the right according to the exponent difference between the two operands, and aligns it with the mantissa of the operand with a large exponent. The adder reads two operands from the pair-order part to add, and inputs the addition result to the leading zero counting part and the normalized shifting part; the leading zero counting part calculates the number of leading zeros according to the addition result, and puts the l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com