Semiconductor device and manufacturing method thereof

一种制造方法、半导体的技术,应用在半导体/固态器件制造、半导体器件、半导体/固态器件零部件等方向,能够解决很难均匀分散软磁性体粉末、涡流损失效果变差、电路短路等问题,达到低价格、降低涡流损失、均匀涡流损失的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

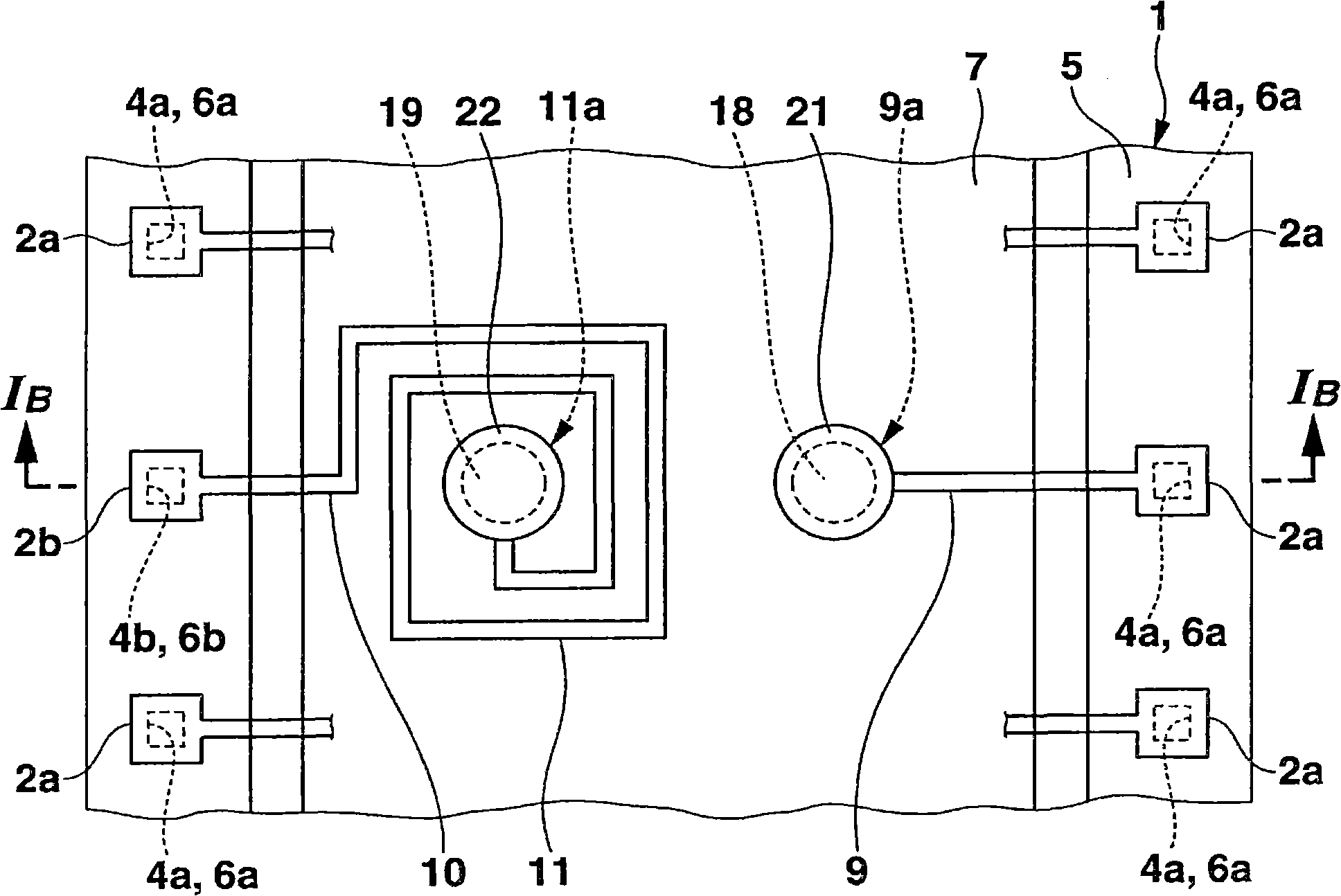

[0035] Figure 1A It is a plan view showing main parts of the semiconductor device according to the first embodiment of the present invention (excluding Figure 1B The state behind the sealing film in).

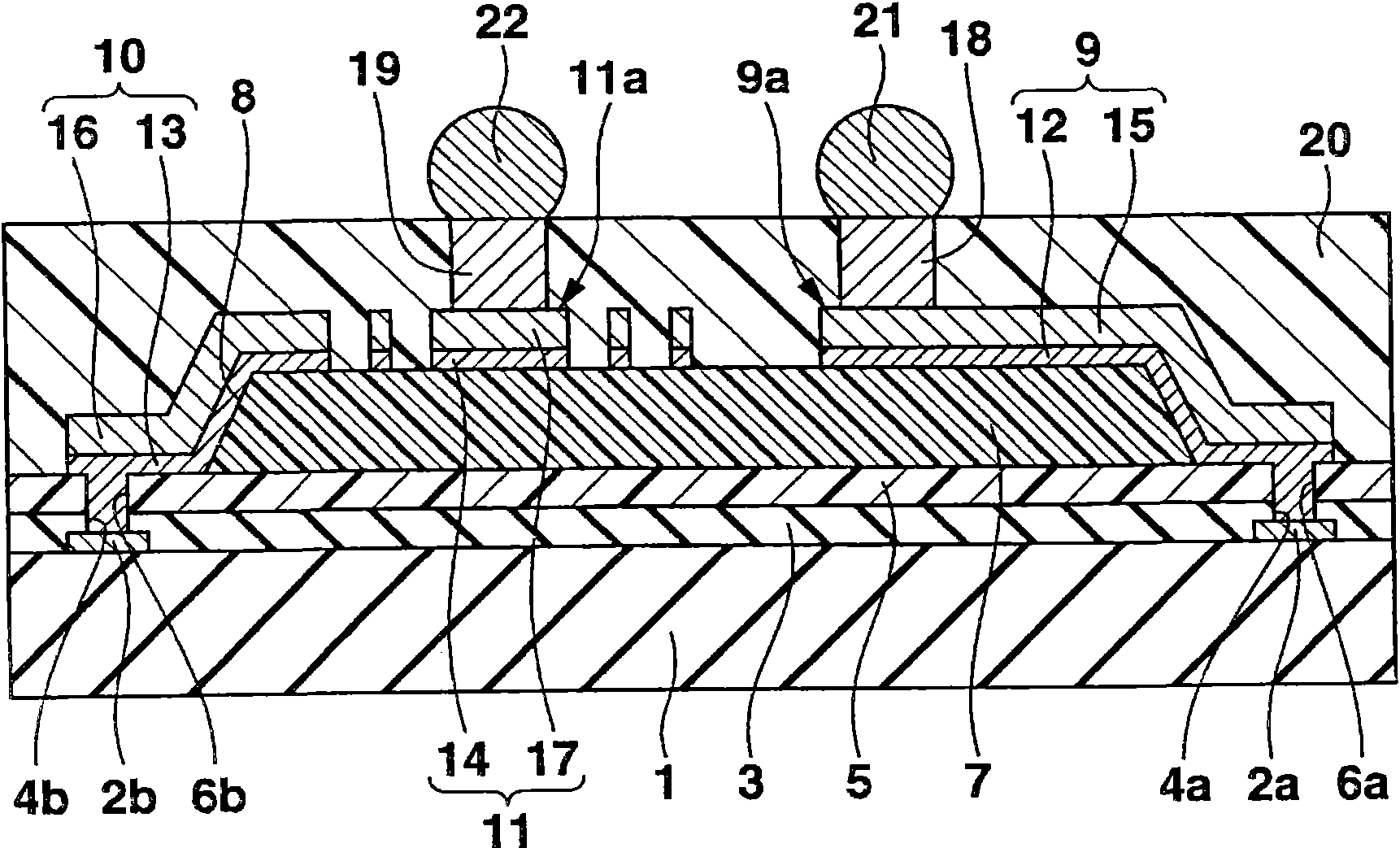

[0036] Figure 1B is along Figure 1A Sectional view of the B-B line.

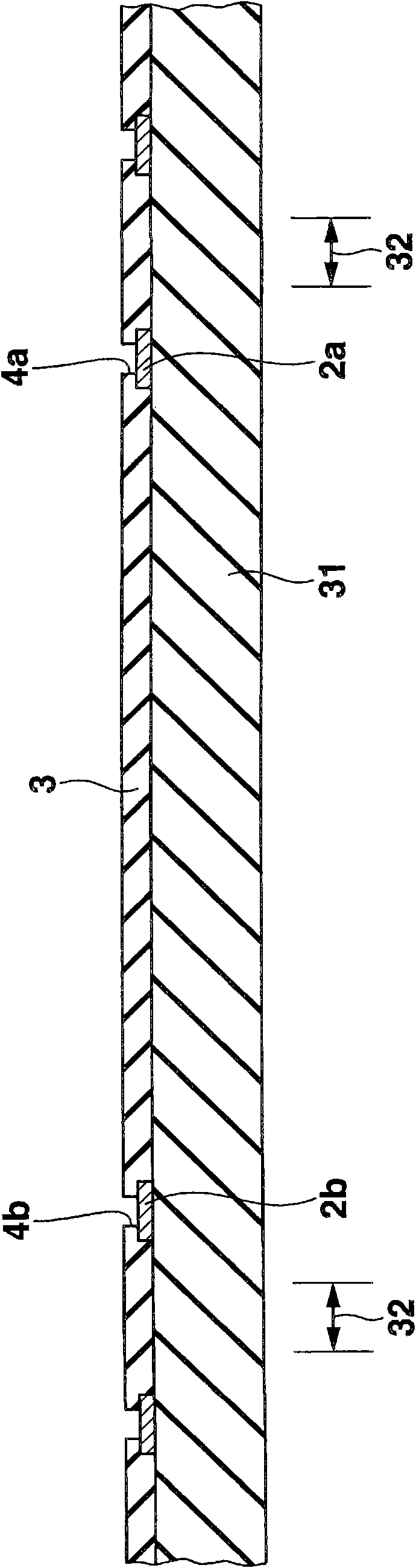

[0037] This semiconductor device has a planar square silicon substrate (semiconductor substrate) 1 generally called a CSP. On the upper surface of the silicon substrate 1, elements for forming an integrated circuit with predetermined functions, such as circuit elements (not shown) such as transistors, diodes, resistors, and capacitors, are formed. A plurality of connection pads 2a, 2b constituted by etc., and the plurality of connection pads 2a, 2b are connected to the integrated circuit. In this case, the connection pad indicated by reference numeral 2b is a member connected to the outer end of the spiral-shaped thin film sensor element 11 described later.

[0038] A passivation film 3 made of silico...

no. 2 approach

[0065] Figure 13A is a plan view of the main part of the semiconductor device according to the second embodiment of the present invention (excluding Figure 13B The state behind the sealing film in).

[0066] Figure 13B It is a cross-sectional view along line B-B.

[0067] In this semiconductor device, withFigure 1A , 1B The big difference of the shown semiconductor device is that not only the outer end of the spiral-shaped thin film sensing element 11, but also the inner end is connected to the integrated circuit (not shown) formed on the upper surface of the silicon substrate 1. ) connection pads are connected.

[0068] That is, the connection pads indicated by reference numerals 2b and 2c are connected to the inner end and the outer end of the spiral-shaped thin film induction element 13, and Figure 13A are arranged adjacently. A passivation film 3 is provided on the upper surface of the silicon substrate 1 except the central portions of the connection pads 2a, 2b,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com