Flying scoreboard device for controlling out-order transmission in superscale microprocessor

A microprocessor and scoreboard technology, applied in machine execution devices, concurrent instruction execution, etc., can solve the problems of waste of area and power consumption, long delay of physical register state table, etc., to reduce area and power consumption, The effect of shortening the critical path delay and improving the energy consumption ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

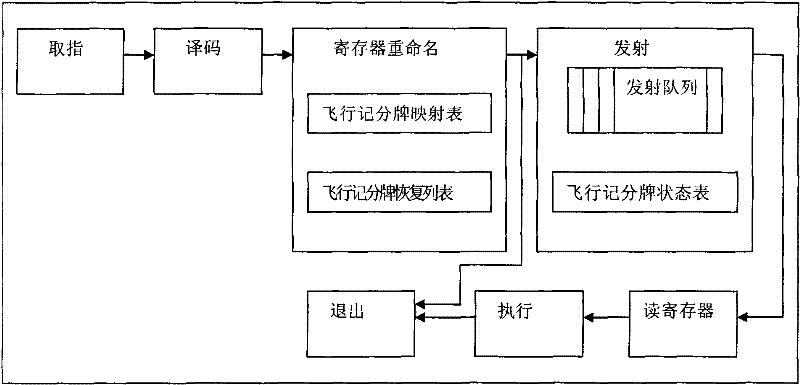

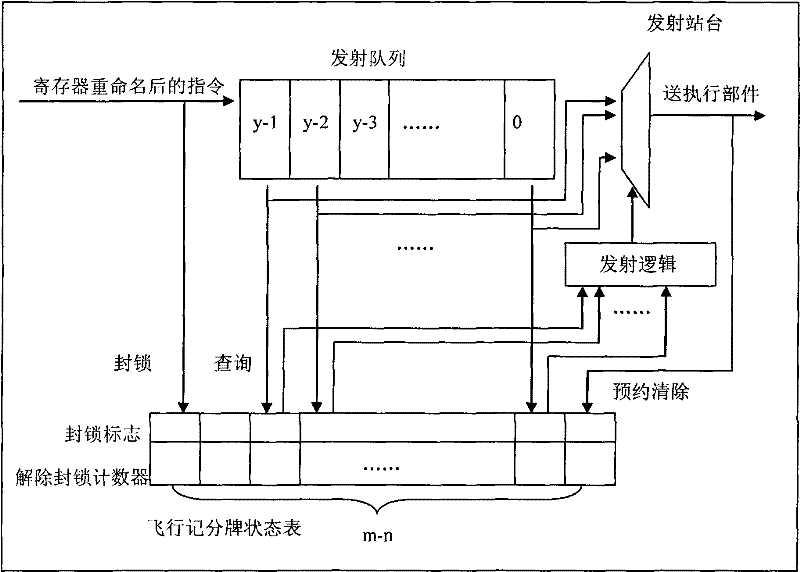

[0014] Such as figure 1 As shown, the device of the present invention needs to set a flight scoreboard mapping table and a flight scoreboard recovery list at the register renaming station, and set a flight scoreboard status table at the launch station.

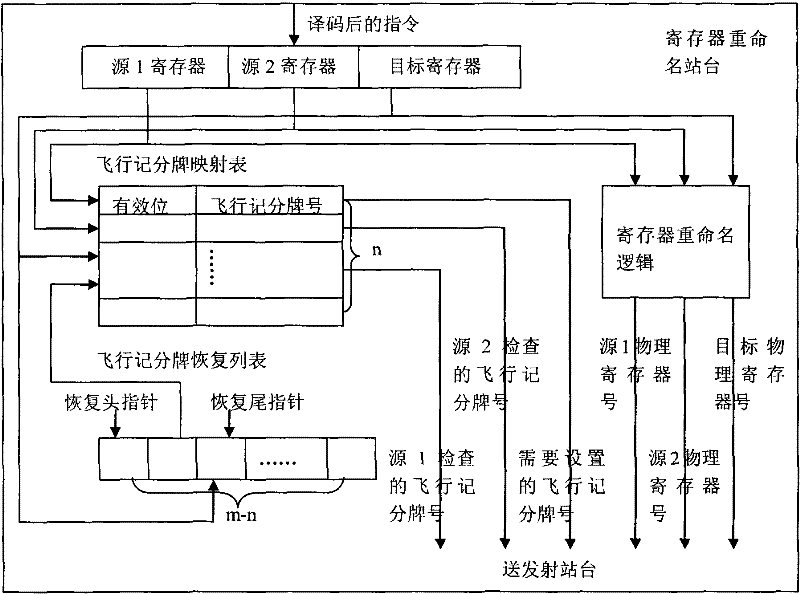

[0015] Such as figure 2 As shown, the flight scoreboard mapping table records the nearest mapping relationship between logic registers and flight scoreboards. The number of entries is equal to the number of logic registers (n). scoreboard with log 2 (m-n) bit representation. If the effective bit is "0", it means that the source register of the instruction has already been prepared, and there is no need to query the flight scoreboard status table when the instruction is launched; It is necessary to query the flight scoreboard status table.

[0016] Such as figure 2 As shown, the flight scoreboard recovery list records the last mapping relationship between the target logic registers of all flight instructions and the flig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com