Error protection method, tdc module, ctdc module, and calibration method thereof

A time-to-digital conversion, all-digital phase-locked loop technology, applied in the direction of analog/digital conversion, code conversion, instruments, etc., can solve the problems of error propagation, and the analog phase-locked loop is prone to errors, and achieves the effect of reducing errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

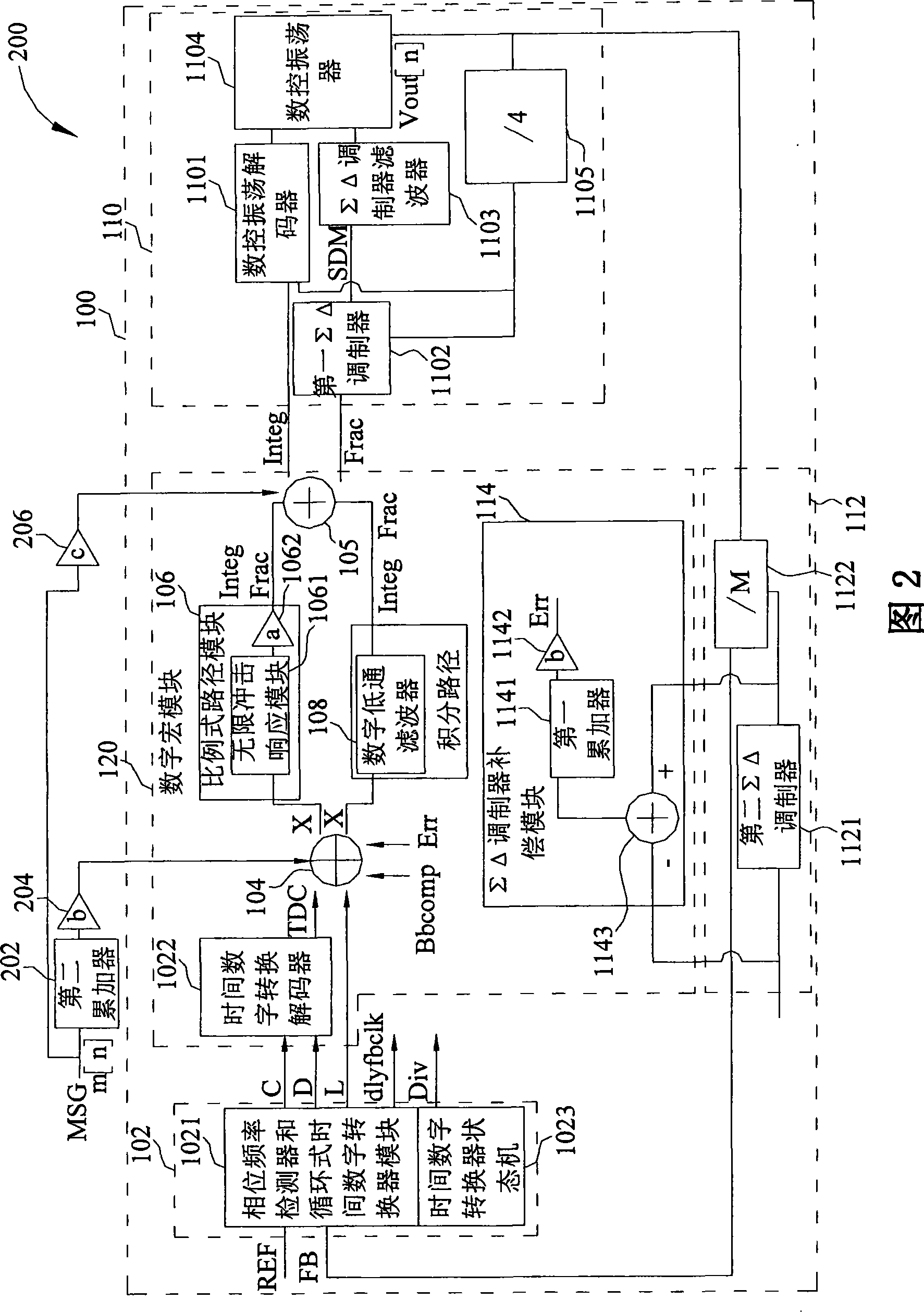

[0025] The present invention discloses an all-digital phase-locked loop for direct frequency modulation and having fine gaincalibration (Fine gaincalibration), wherein the all-digital phase-locked loop uses some components disclosed by the inventor (such as the disclosed by the inventor digitally controlled oscillator) with technical characteristics. Through the all-digital phase-locked loop disclosed in the present invention, the switching noise can be greatly reduced, and the loop gain of the all-digital phase-locked loop can also be precisely fine-tuned. Through the numerically controlled oscillator disclosed in the present invention, precise frequency resolution can be achieved in the disclosed all-digital phase-locked loop.

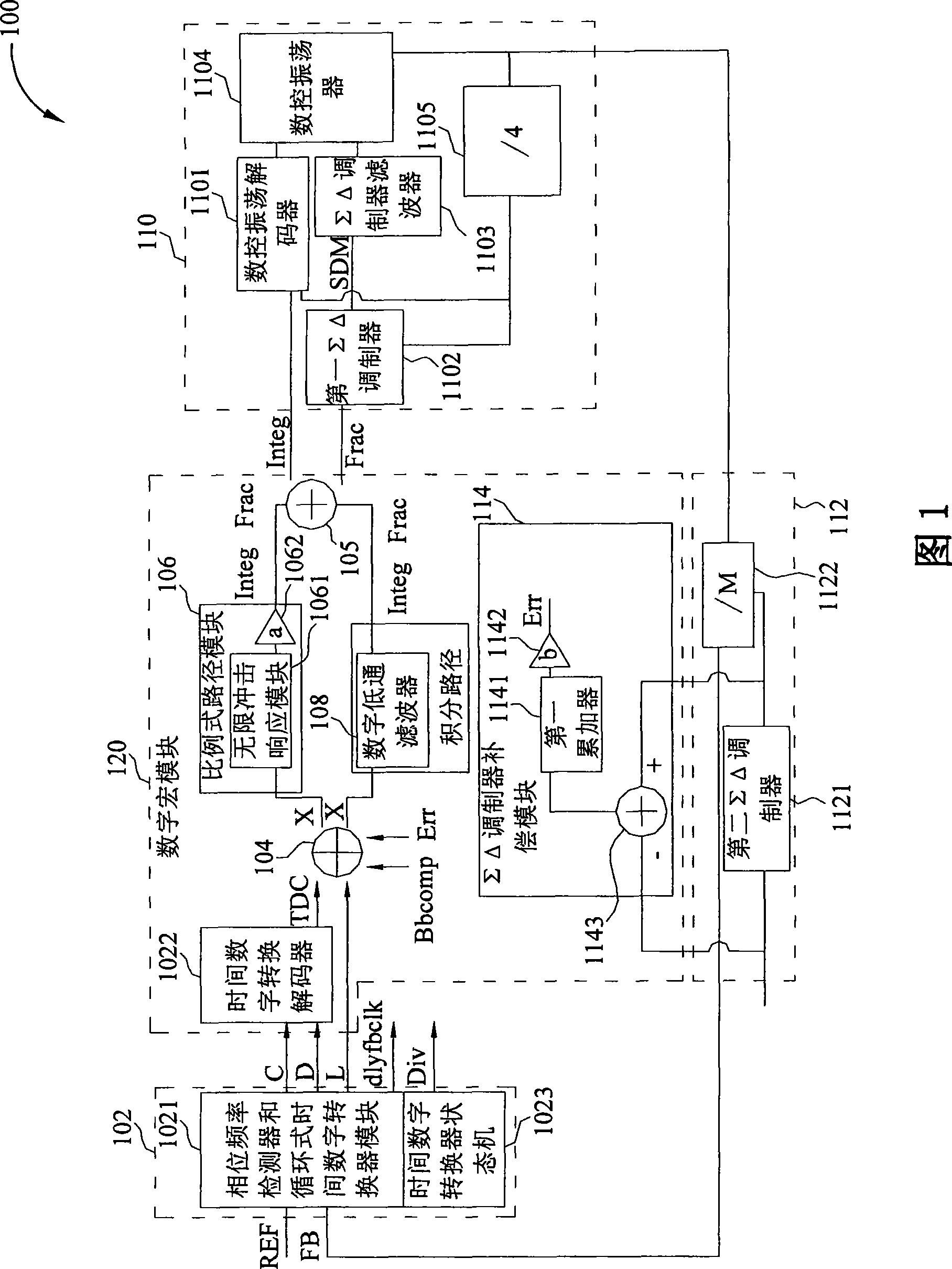

[0026] Please refer to FIG. 1 , which is a schematic diagram of an all-digital phase-locked loop 100 disclosed in an embodiment of the present invention. As shown in FIG. 1 , an all-digital phase-locked loop 100 includes a time-to-digital converter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com