Routing node microstructure for on-chip network

A network-on-chip and microstructure technology, applied in data exchange network, data exchange details, digital transmission system, etc., can solve problems such as component communication bottleneck effect, transistor quantity limitation, SoC chip performance limitation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

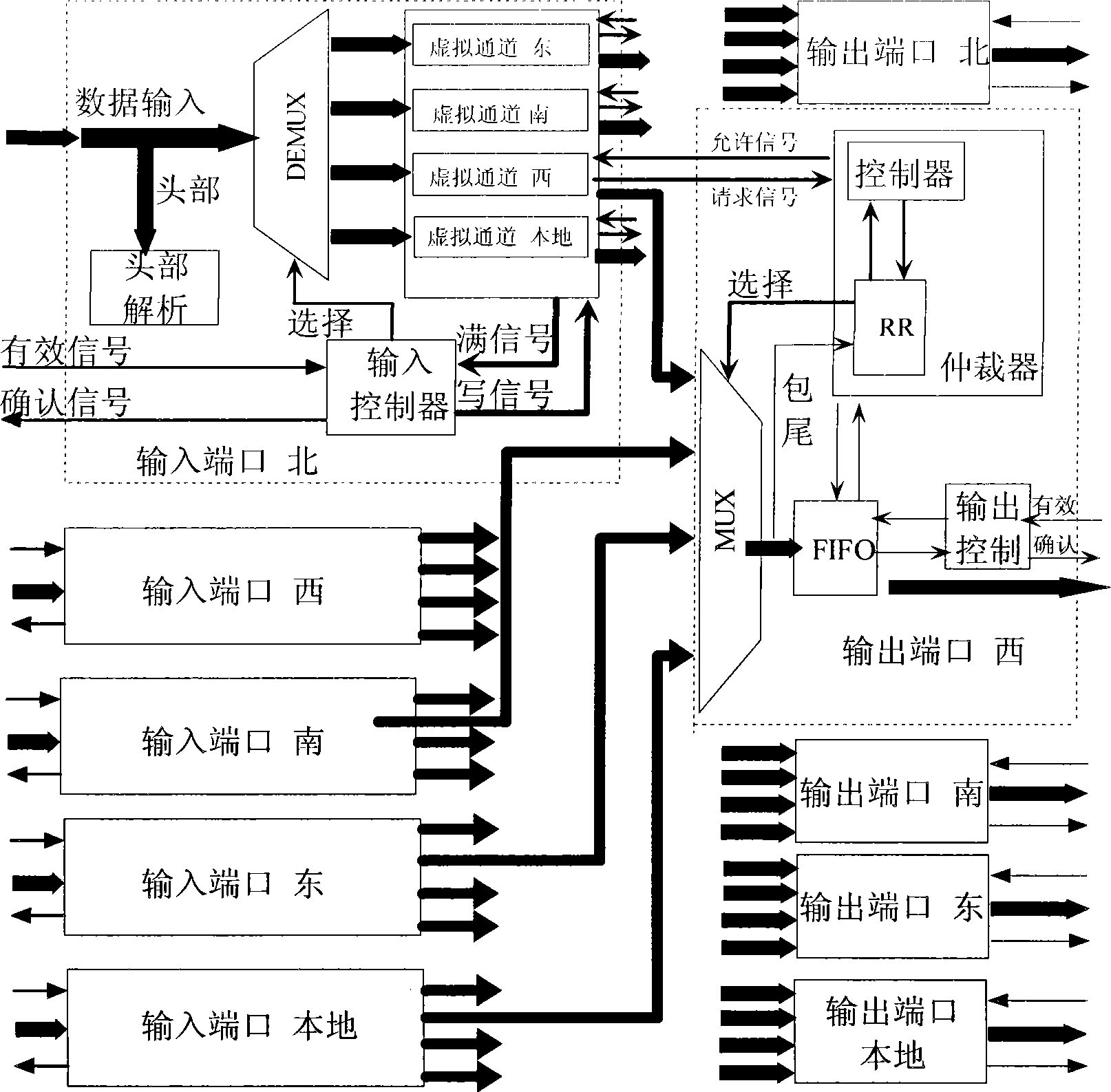

[0063] Hereinafter, the present invention will be specifically described by taking an input module and an output module composed of standard 5 output ports and 5 input ports as an example.

[0064] In terms of hardware, the input module is composed of 5 input ports, which respectively represent 5 directions of east, south, west, north and local, and the local direction is connected to the local processor.

[0065] figure 1 The dotted line in the middle indicates the structural diagram of the north-to-west transmission of the input port to the west of the output port, and the transmission between other ports is the same as figure 1 The dotted line part has the same structure.

[0066] Such as figure 1 As shown, in the present invention, when a data packet is to be transmitted from the upper-level node to the current node, the header flit carrying routing information of the data packet is first sent to the current node as a request signal. After the current node receives t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com