Instruction set optimization

A technology of instruction and instruction memory, which is applied in the field of instruction set optimization and can solve the problem of waste of storage space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

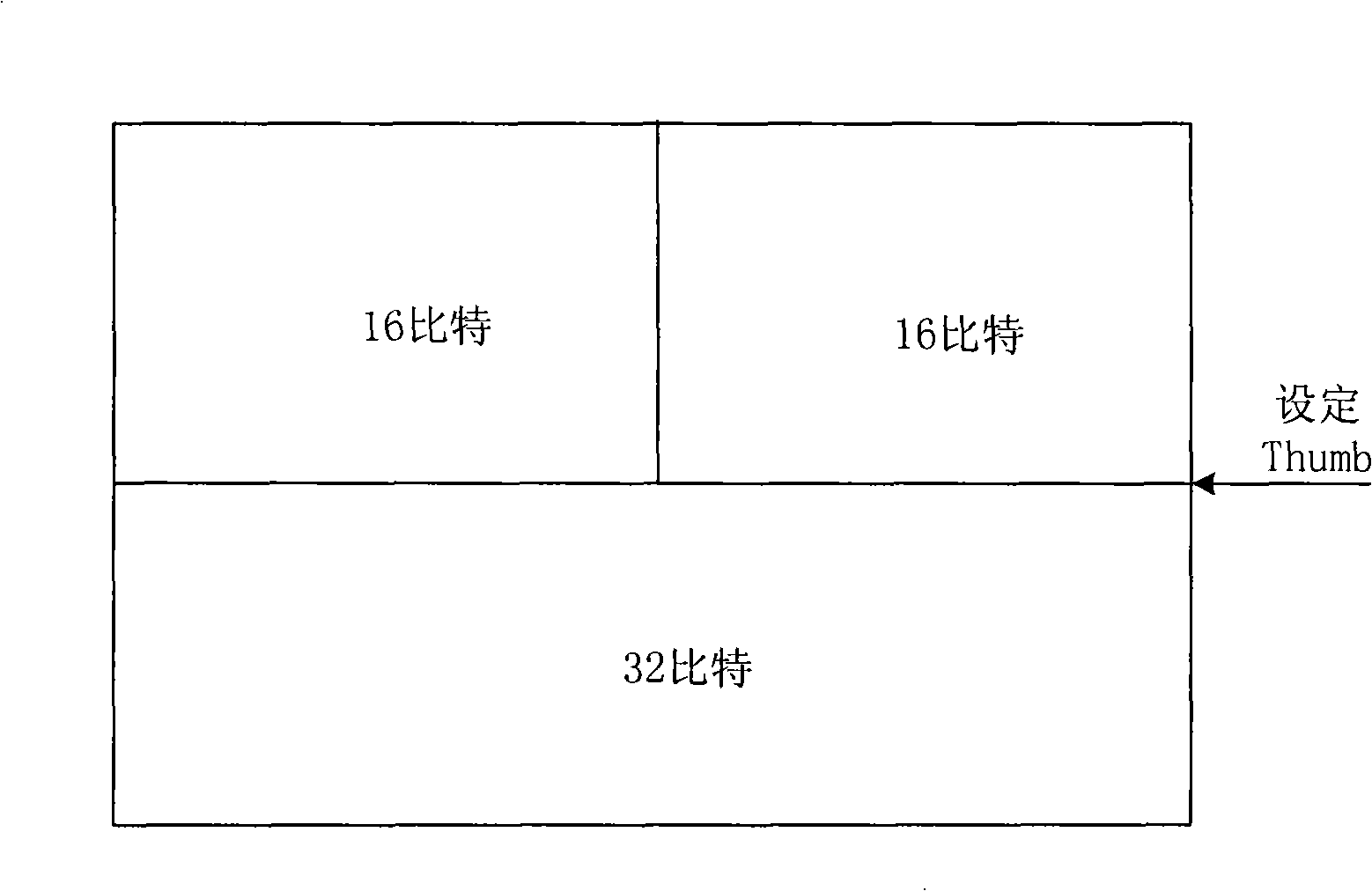

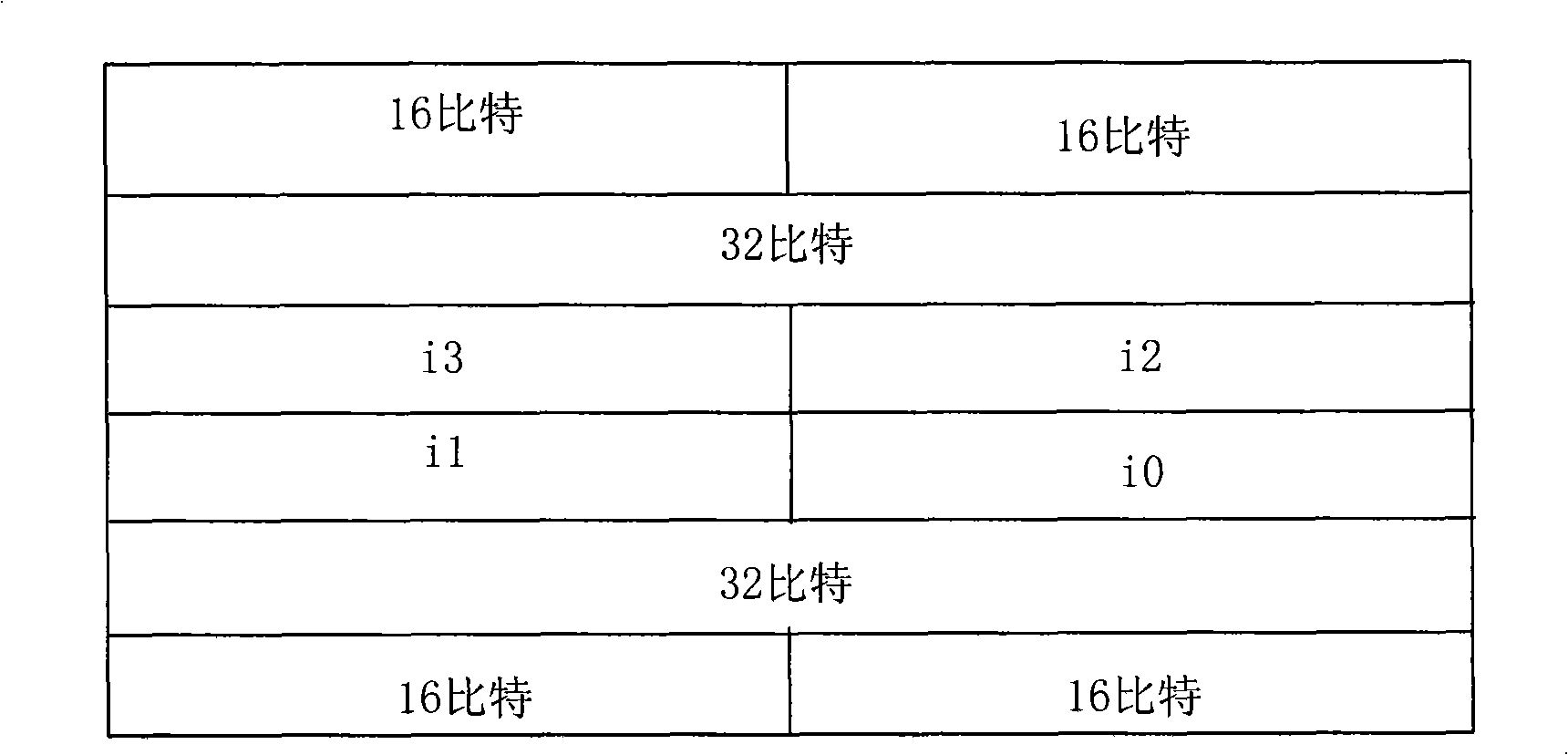

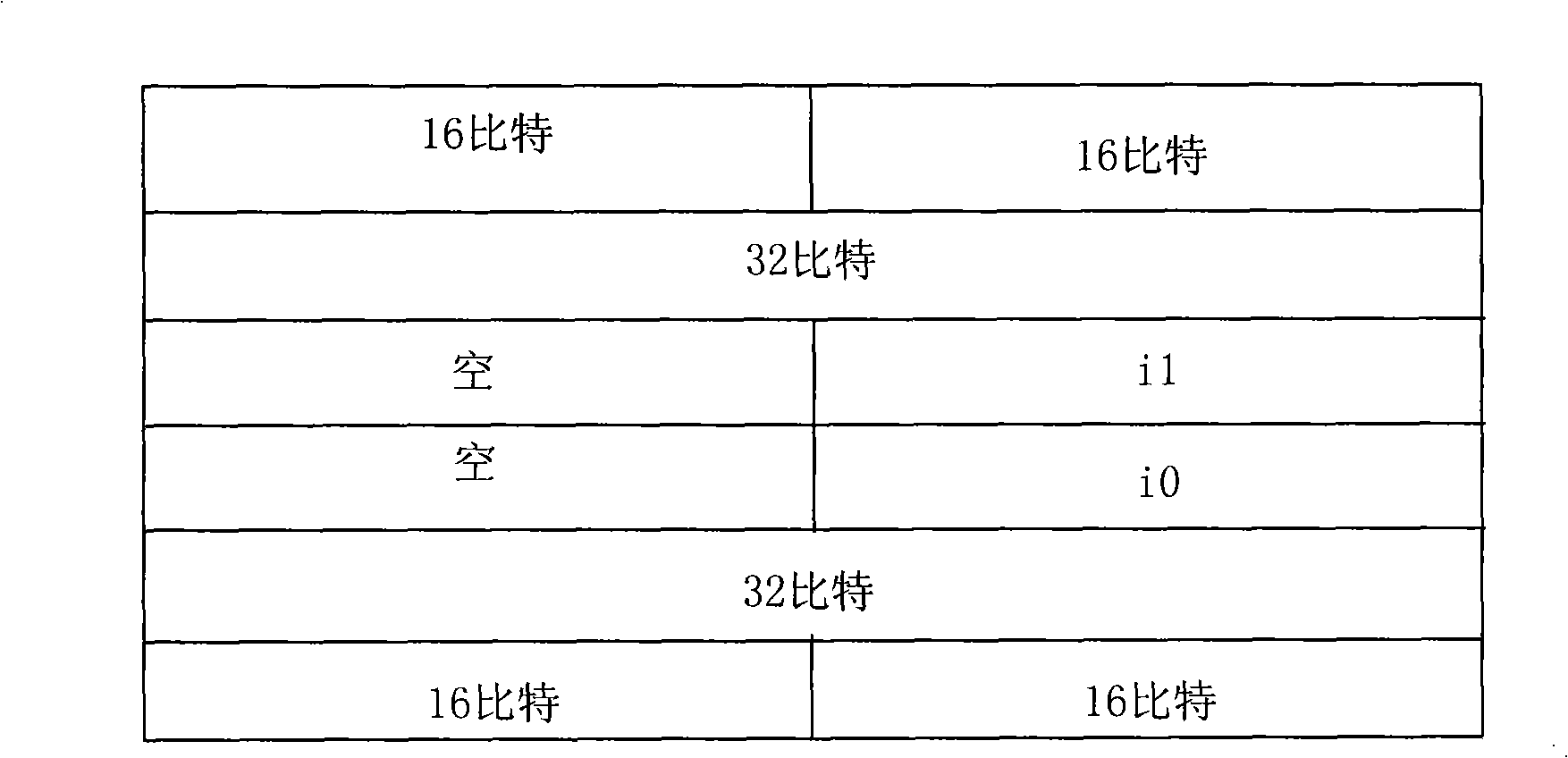

[0019] image 3 is a diagram of the instruction format according to one embodiment of the present invention. Such as image 3 As shown, there is a 32-bit storage space. The 32-bit storage space may store one 32-bit instruction, or two 16-bit instructions. When decoding, first treat the 32-bit word as a 32-bit instruction, and check bits 27-31. If bits 27-31 are not the opcode of a 16-bit instruction, it indicates a 32-bit instruction. If there is an opcode for a 16-bit instruction at bits 27-31, it indicates that the upper 16 bits (bits 16-31) of the 32-bit word belong to a 16-bit instruction. Obviously, the lower 16 bits (bits 0-15) of a 32-bit word also belong to a 16-bit instruction, so the lower 16 bits are decoded into another 16-bit instruction.

[0020] It should be noted that the operation code is not only set in the upper 5 bits of 16 bits. It can be set at any position of 16 bits, and can also be composed of a certain number of bits.

[0021] According to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com