Method and system for calculating delayed statistics variation caused by coupling event between two adjacent networks in integrated circuit design

A technology of integrated circuits and adjacent networks, applied in the field of statistical computing, can solve problems such as low efficiency, pessimism, and variation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The invention and its various features and advantages are elucidated with reference to the non-limiting embodiments shown in the drawings and described in detail in the following description. It should be noted that the features shown in the drawings are not necessarily drawn to scale. Descriptions of well-known components and processing techniques are omitted so as not to unnecessarily obscure a detailed understanding of the present invention.

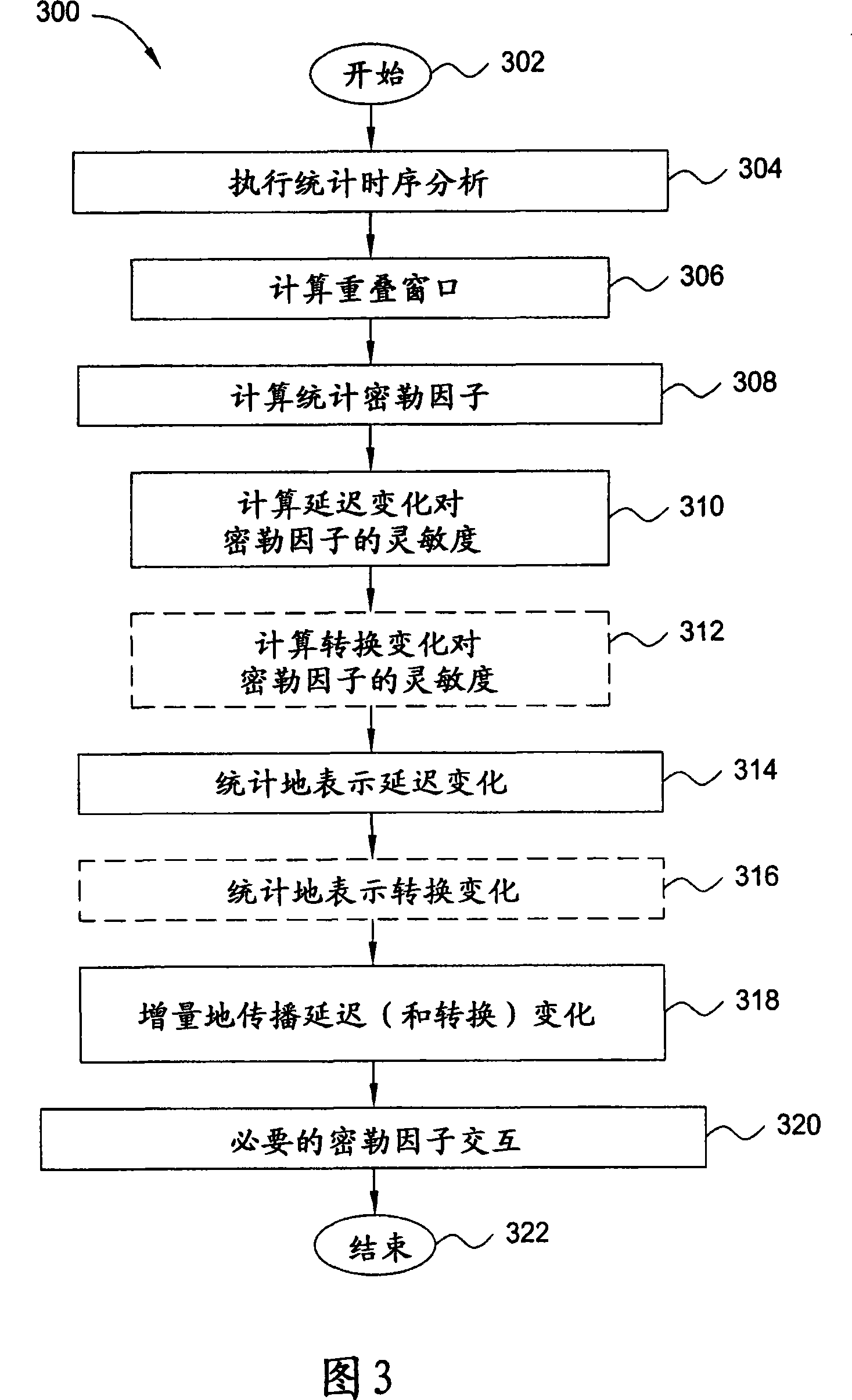

[0025] image 3 is a flowchart showing one embodiment of a static timing analysis method 300 for an integrated circuit design according to the present invention. Method 300 can be implemented to analyze combinational integrated circuit designs and sequential integrated circuit designs. As will be described in detail below, the method 300 accurately and efficiently handles process variation and coupling events in the static timing analysis process, while also considering complex dependencies introduced by the process variation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com