A device and method for FPGA simulation

A simulation and parameter configuration technology, applied in the field of data communication, can solve the problems of long verification time and low efficiency, and achieve the effects of simple error diagnosis, reduced processing time, and improved efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

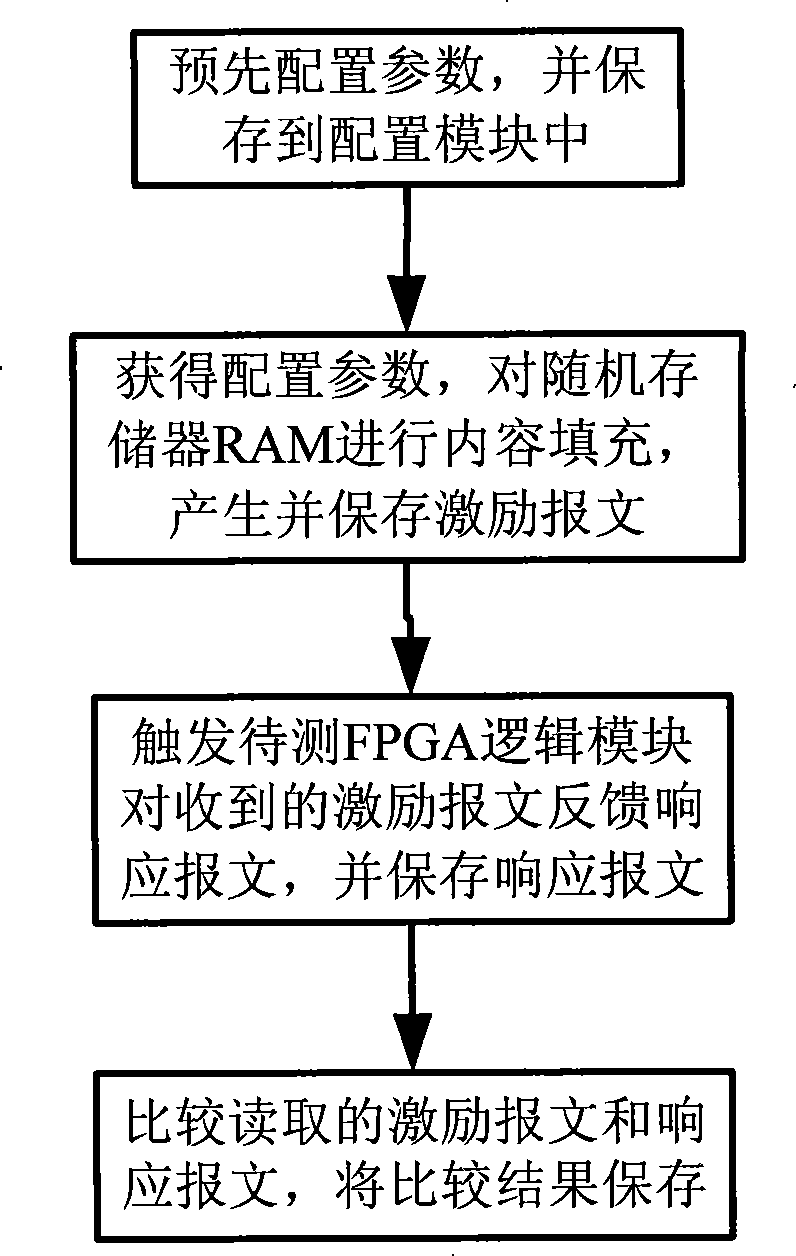

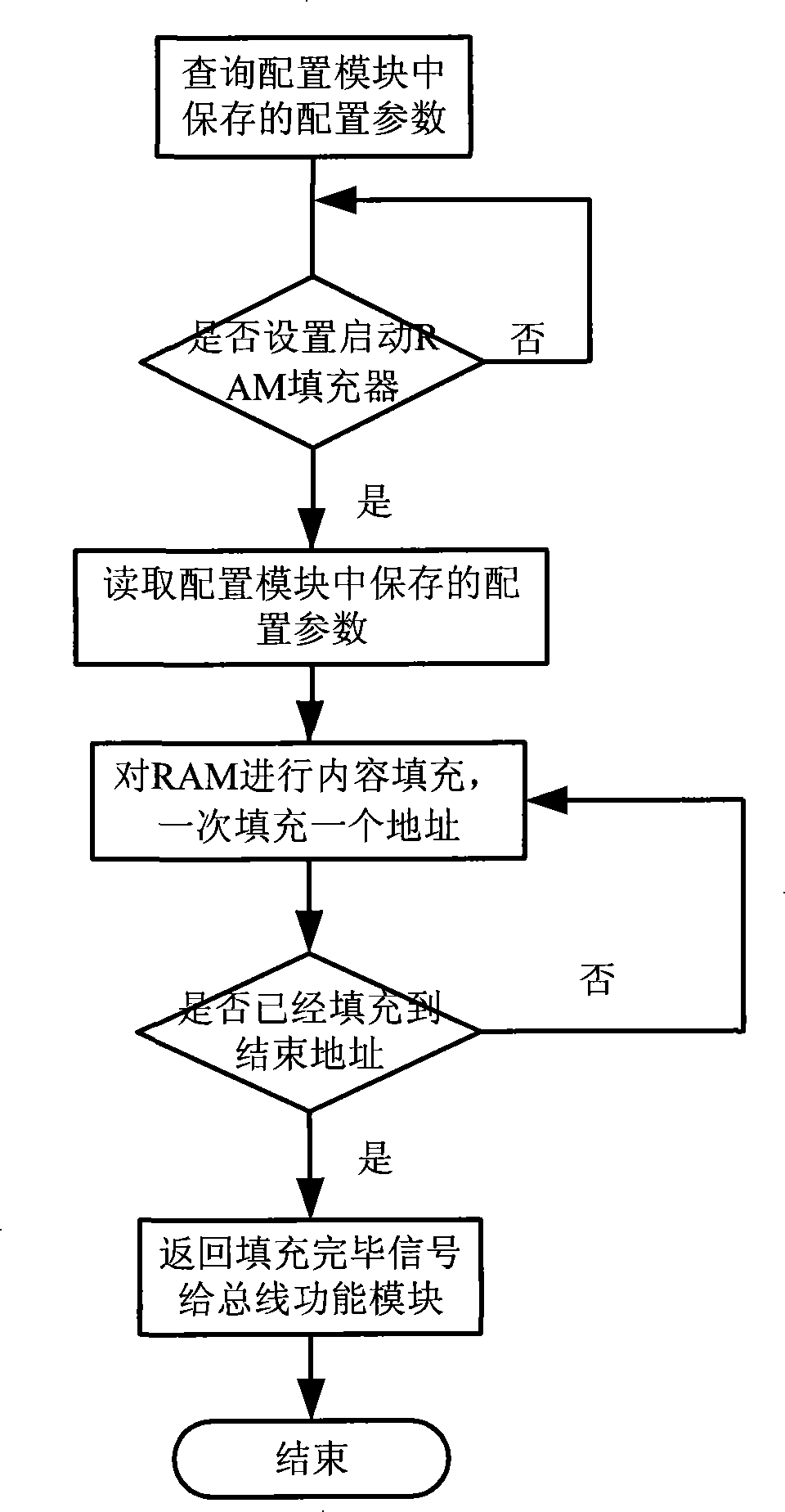

[0058] The basic technical idea of the present invention is that when the FPGA logic module to be tested is simulated and verified, a RAM filling module is introduced to directly fill the content of the random access memory RAM according to random design requirements, without the need for the FPGA logic module to be tested according to the The timing requires reading and writing of preset data, which greatly reduces the time for simulation verification of the FPGA logic module to be tested, and greatly improves the efficiency of simulation verification of the FPGA logic module to be tested.

[0059] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

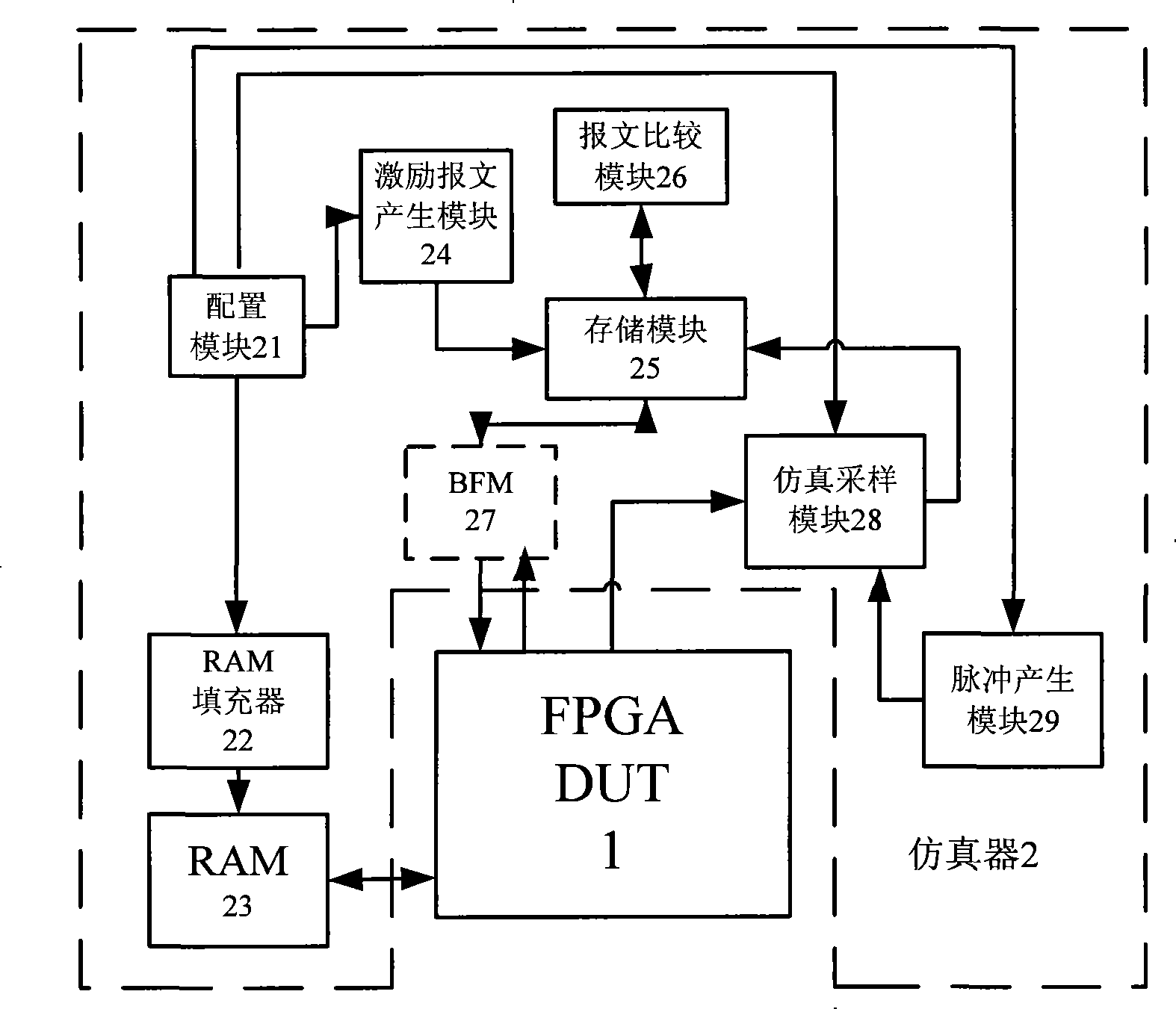

[0060] Such as figure 1 Shown is the structural diagram of a specific embodiment of the device of the present invention, comprises as shown in the figure: FPGA logic module to be tested (FPGA's DUT) 1 and emulator (TESTBENCH) 2, described FPGA ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com