Semiconductor integrated circuit and multi-chip module

A technology of integrated circuits and semiconductors, applied in the direction of semiconductor devices, circuits, semiconductor/solid-state device components, etc., can solve the problems of reducing the area, weakening the area reduction effect, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

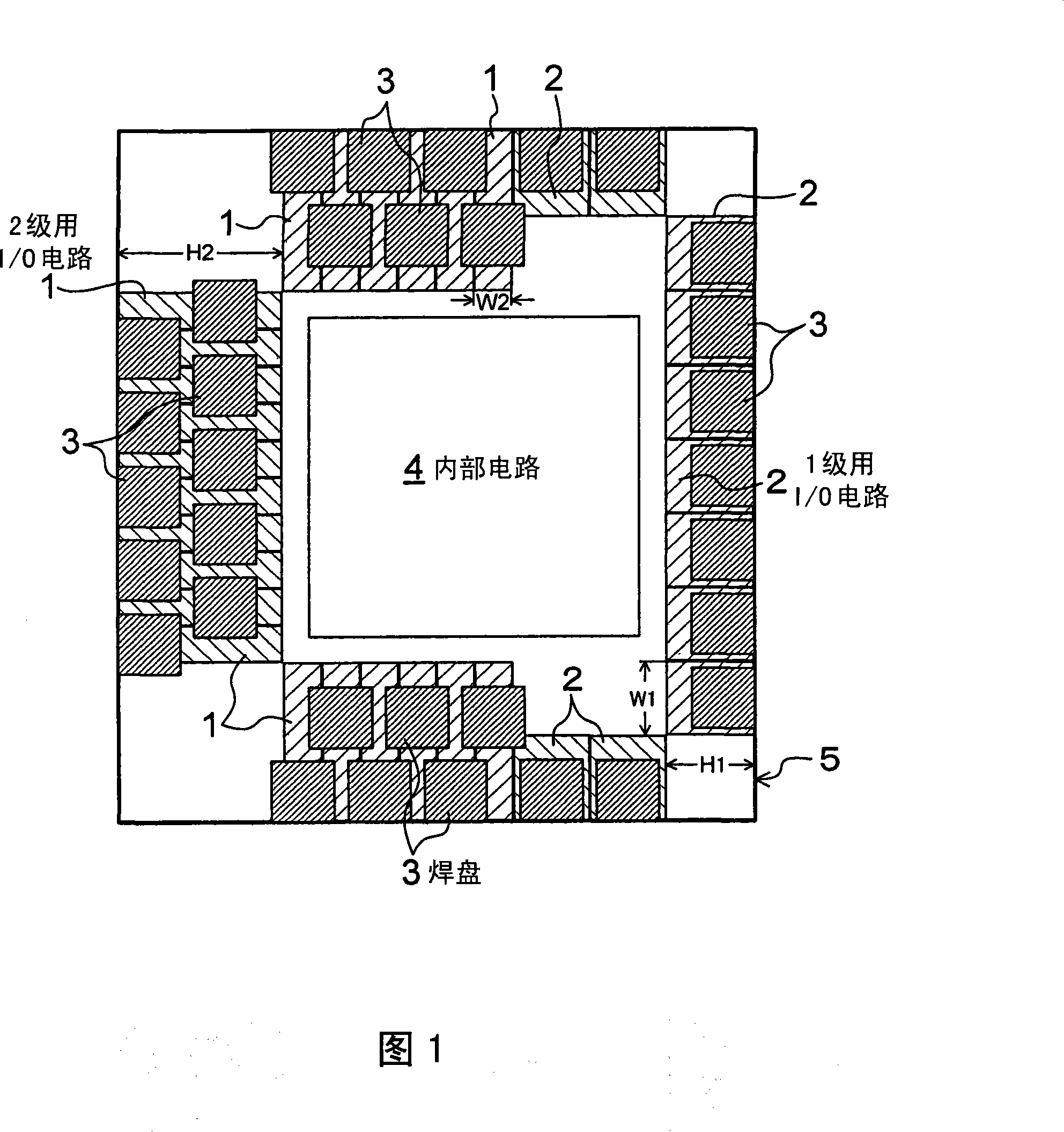

[0077] FIG. 1 shows the semiconductor integrated circuit of this embodiment.

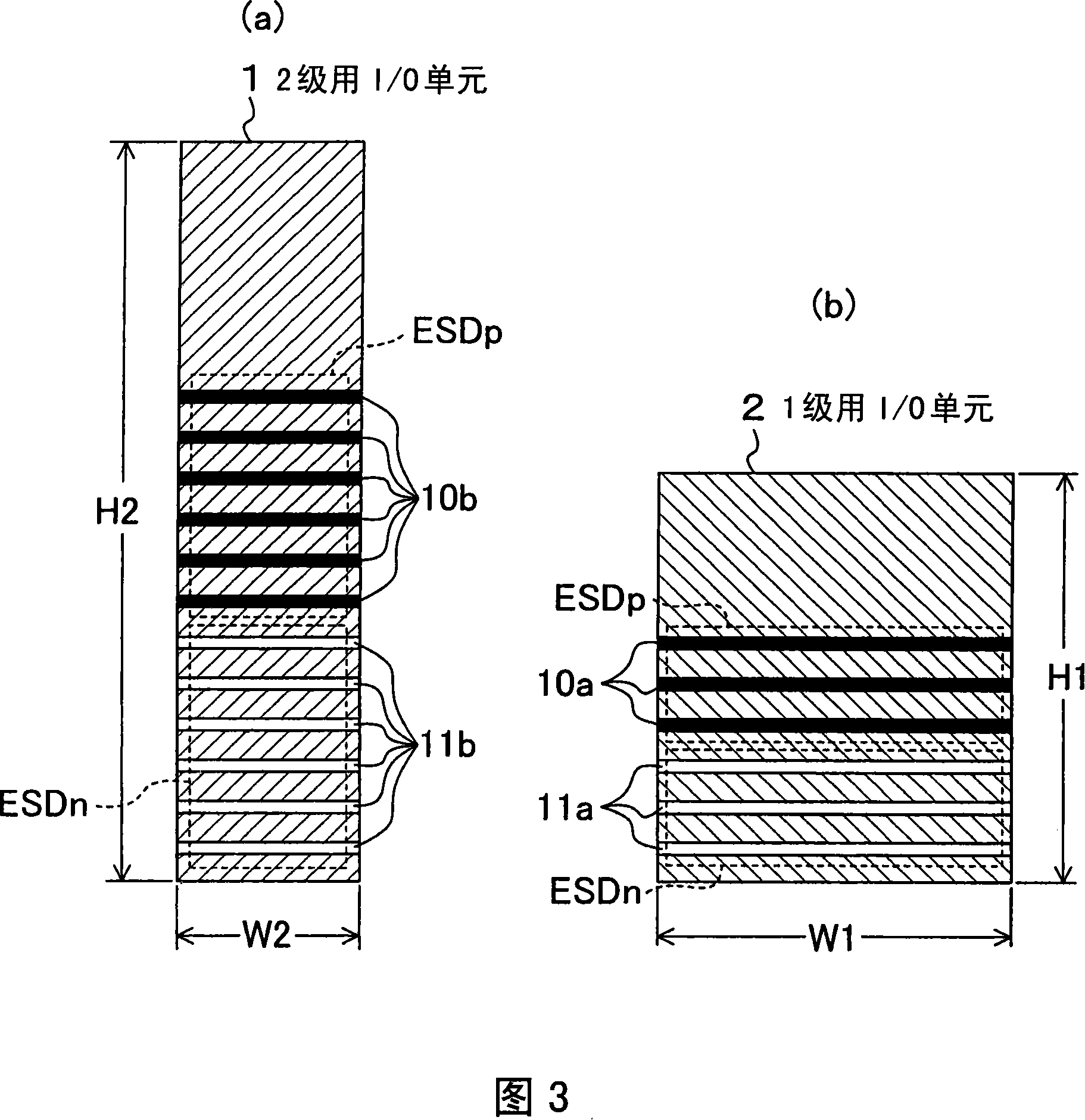

[0078] A semiconductor integrated circuit 5 serving as a semiconductor chip in the figure has a rectangular shape, and an internal circuit 4 is provided in the center. On the outside of the above-mentioned internal circuit 4, a plurality of I / O circuits 1, 2 are provided along the four sides of the outer periphery. These I / O circuits are used to output signals of the internal circuit 4 to the outside or input external signals to the internal circuit 4, and the pads 3 are provided thereon.

[0079] There are two kinds of the above-mentioned plurality of I / O circuits. The I / O circuit 1 is an I / O circuit for m (m=2) stages in which two pads 3 can be arranged in a direction facing the above-mentioned internal circuit 4. The O circuit 2 is an I / O circuit for n (n=1 (n

no. 2 Embodiment approach

[0089] Next, a second embodiment of the present invention will be described.

[0090] FIG. 8 shows the semiconductor integrated circuit of this embodiment. In this semiconductor integrated circuit, the I / O circuit 1 for the second stage is provided on the upper side, the lower side, and the left side, and the I / O circuit 2 for the first stage is provided on the right side. At the corners C of the lower right part and the upper right part of the semiconductor integrated circuit 5, there are provided power supply wirings for switching the power supply wiring between the I / O circuit 2 for the first stage and the I / O circuit 1 for the second stage. Transit area A. That is, in other words, the present embodiment adopts a structure in which the same type of I / O circuits are provided on each side of the semiconductor integrated circuit 5, and does not change the type of I / O circuits from one side to two levels on one side. For level use or from level 2 use to level 1 use, change th...

no. 3 Embodiment approach

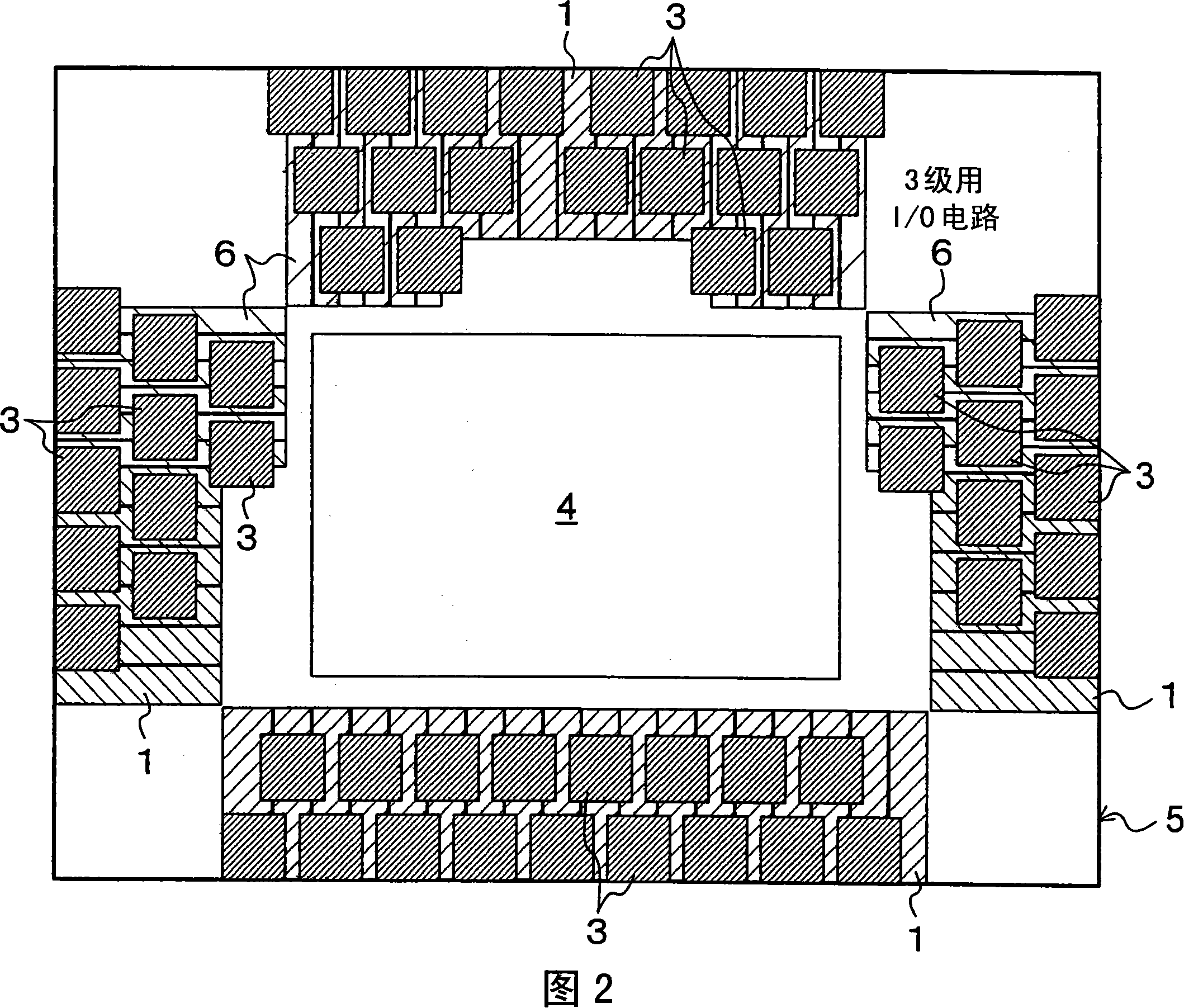

[0095] Next, a third embodiment of the present invention will be described.

[0096] FIG. 12 shows the semiconductor integrated circuit of this embodiment. FIG. 13 shows a view after the pad 3 is removed from the structure of the semiconductor integrated circuit of FIG. 12 . This embodiment takes into account the ease of wire connection when the semiconductor integrated circuit is mounted in a semiconductor package.

[0097] In the semiconductor integrated circuit 5 in the figure, the I / O circuits 2 for the first stage are arrayed on the opposite sides of the upper and lower sides, and the I / O circuits 1 for the second stage are arrayed on the opposite sides of the left and right sides. . Therefore, the power wiring transition area A is provided on all four corners. In other words, the first-level I / O circuits 2 and the second-level I / O circuits 1 are adjacent to each other at each corner, and the second-level I / O circuits 1 are not adjacent to each other.

[0098] Therefo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com