Method for grid connecting with SOI dynamic threshold transistor through anti-off schottky

A technology of transistor and body region, which is applied in the field of silicon-on-insulator dynamic threshold transistor structure where the gate body is connected through a reverse biased Schottky junction, which can solve the problems of incompatibility with ordinary transistors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

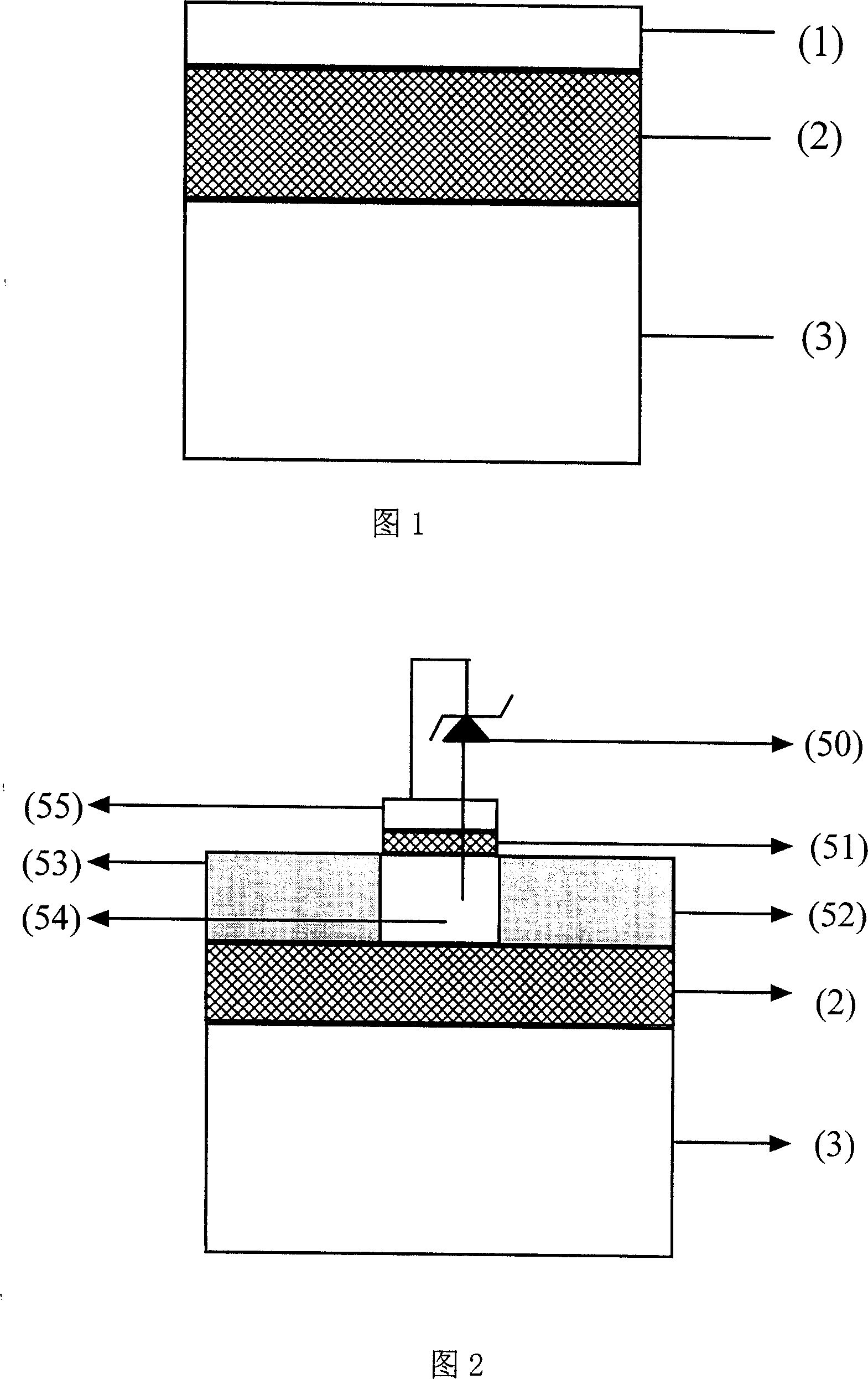

[0015] Figure 1 illustrates a starting SOI silicon wafer that can be used in the present invention. It contains an oxide buried layer (2) to electrically isolate the silicon substrate (3) from the top silicon film (1). A top silicon film (1), in which active device regions can be formed. The SOI silicon wafer can be fabricated by conventional SIMOX (Ion Implantation of Oxygen Ion Isolation) process known to those skilled in the art, or by other conventional processes including, for example, thermal bonding and dicing processes.

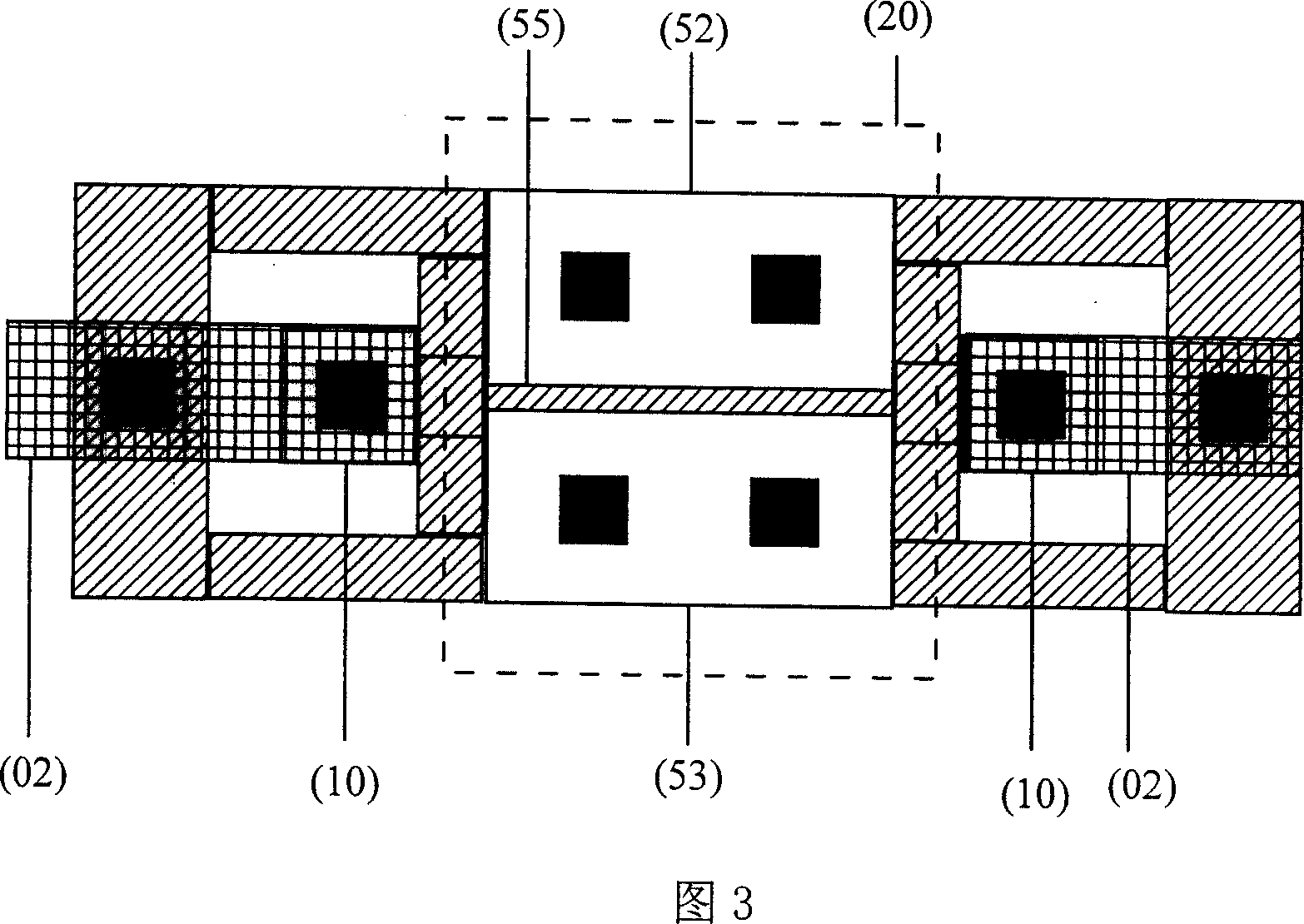

[0016] The present invention utilizes process steps compatible with conventional SOI CMOS processes. In order to electrically isolate the body regions of different devices from each other, isolation techniques such as MESA, STI or LOCOS can be used. When using STI and LOCOS isolation technology, the field oxygen should be in contact with the buried oxide layer.

[0017] Fig. 2 is a kind of structure of silicon-on-insulator dynamic threshold transis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com