Method for demodulating ACK slot signal of HS-DPCCH channel

A technology of signal demodulation and demodulation method, which is applied in the field of wideband code division multiple access WCDMA uplink signal demodulation, and can solve the problems of large SIR estimation deviation and timing offset not considered

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

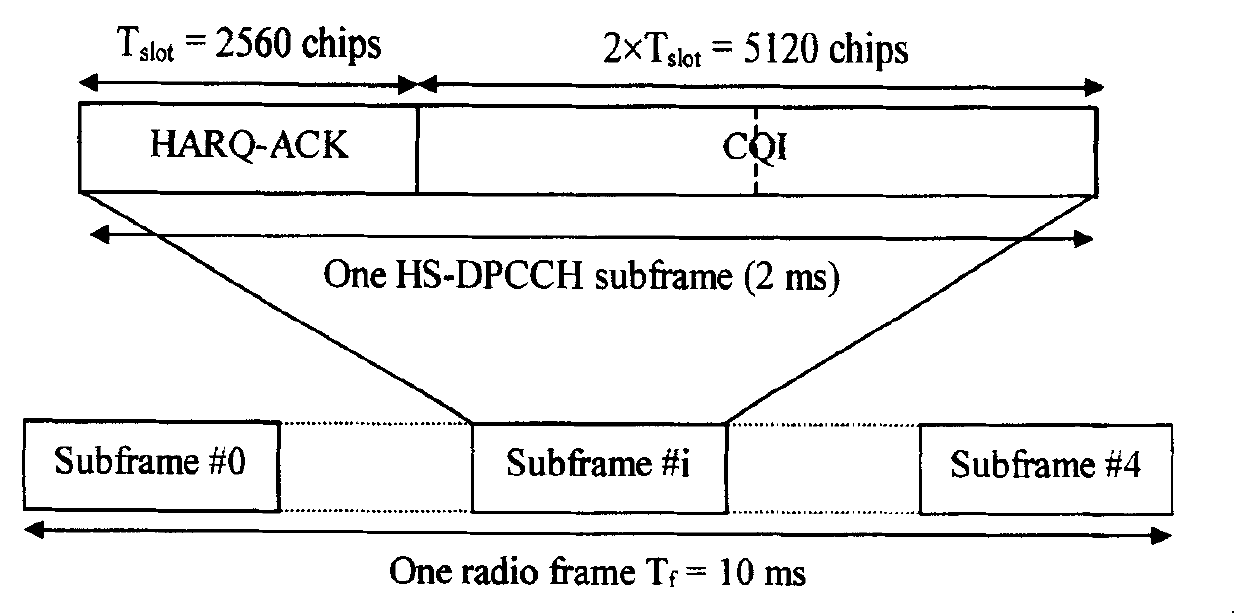

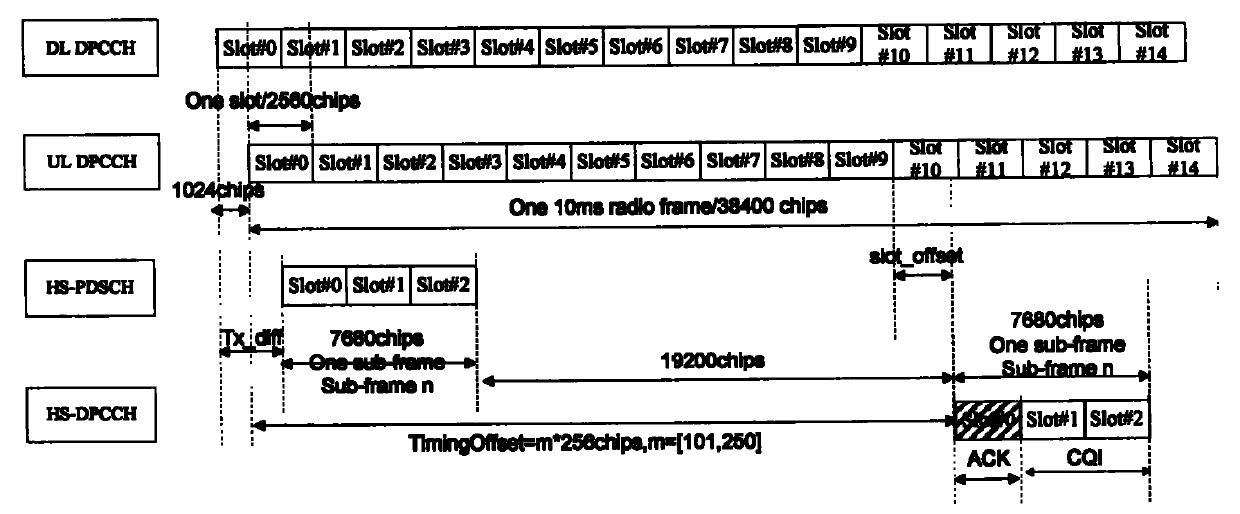

[0050] At first, explain core of the present invention: the SIR estimation method of the ACK time slot of HS-DPCCH channel, comprises the following steps:

[0051] (1) Acquiring input data: interference signal code domain power, ACK slot symbol, channel estimation value power, ACK channel coding mode array, and timing offset between HS-DPCCH channel and uplink DPCCH channel.

[0052] The code domain power of the interference signal refers to the code domain power of the interference signal corresponding to the uplink DPCCH time slot overlapping with the ACK time slot of the HS-DPCCH. If there are two DPCCH time slots overlapping with the ACK time slot of the HS-DPCCH, the input is Code domain power of the interference signal corresponding to the previous DPCCH slot. The code domain power of the interference signal is filtered, and it can be considered that the code domain power of the interference signal in two adjacent time slots remains unchanged in a steady state.

[0053]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com