Manufacturing method of semiconductor package

一种制造方法、半导体的技术,应用在半导体/固态器件制造、半导体器件、半导体/固态器件零部件等方向,能够解决难以谋求作业性的提高、半导体芯片裂纹不良、贯通电极电极材料填充困难等问题,达到提高操作和作业性的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

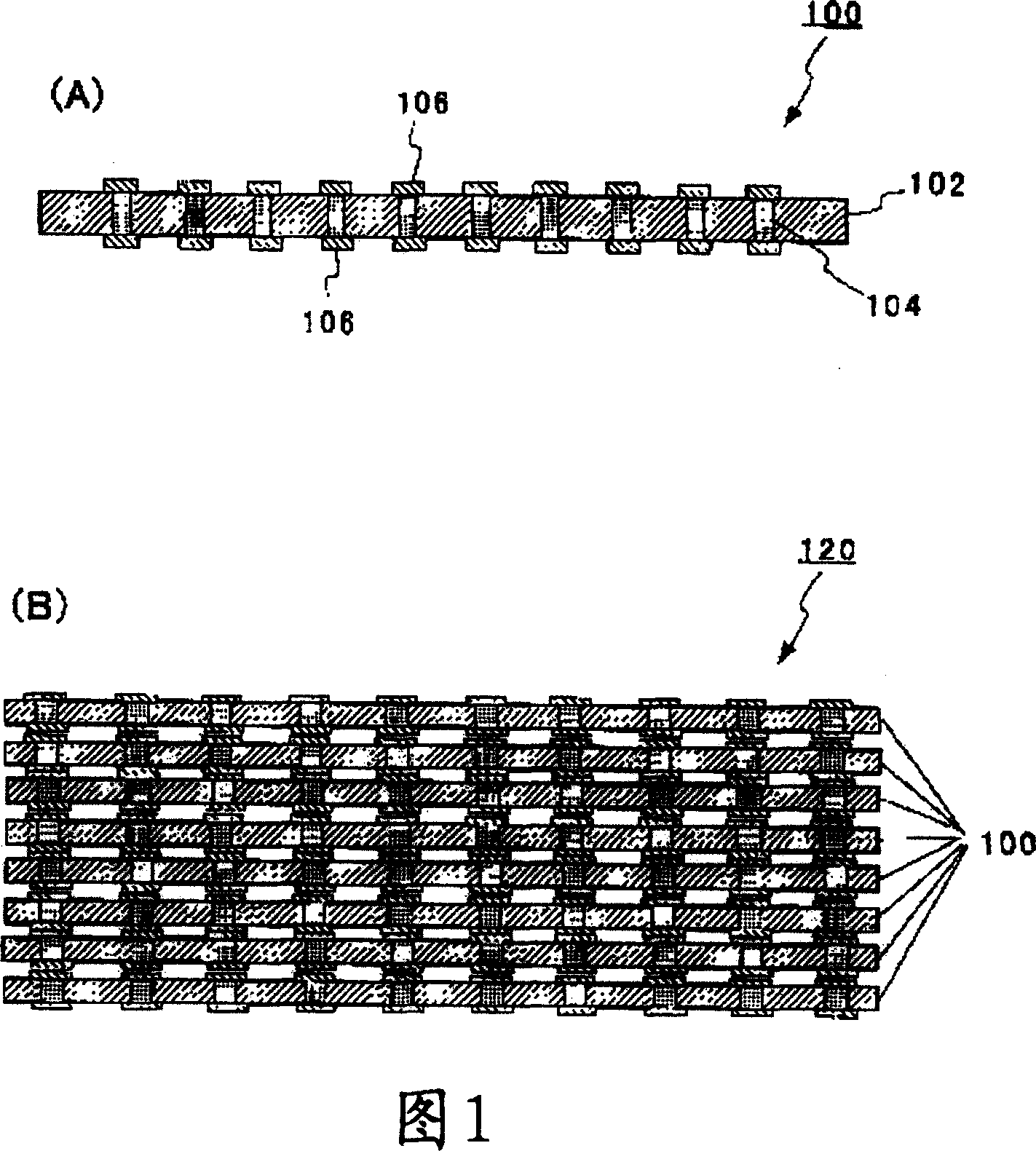

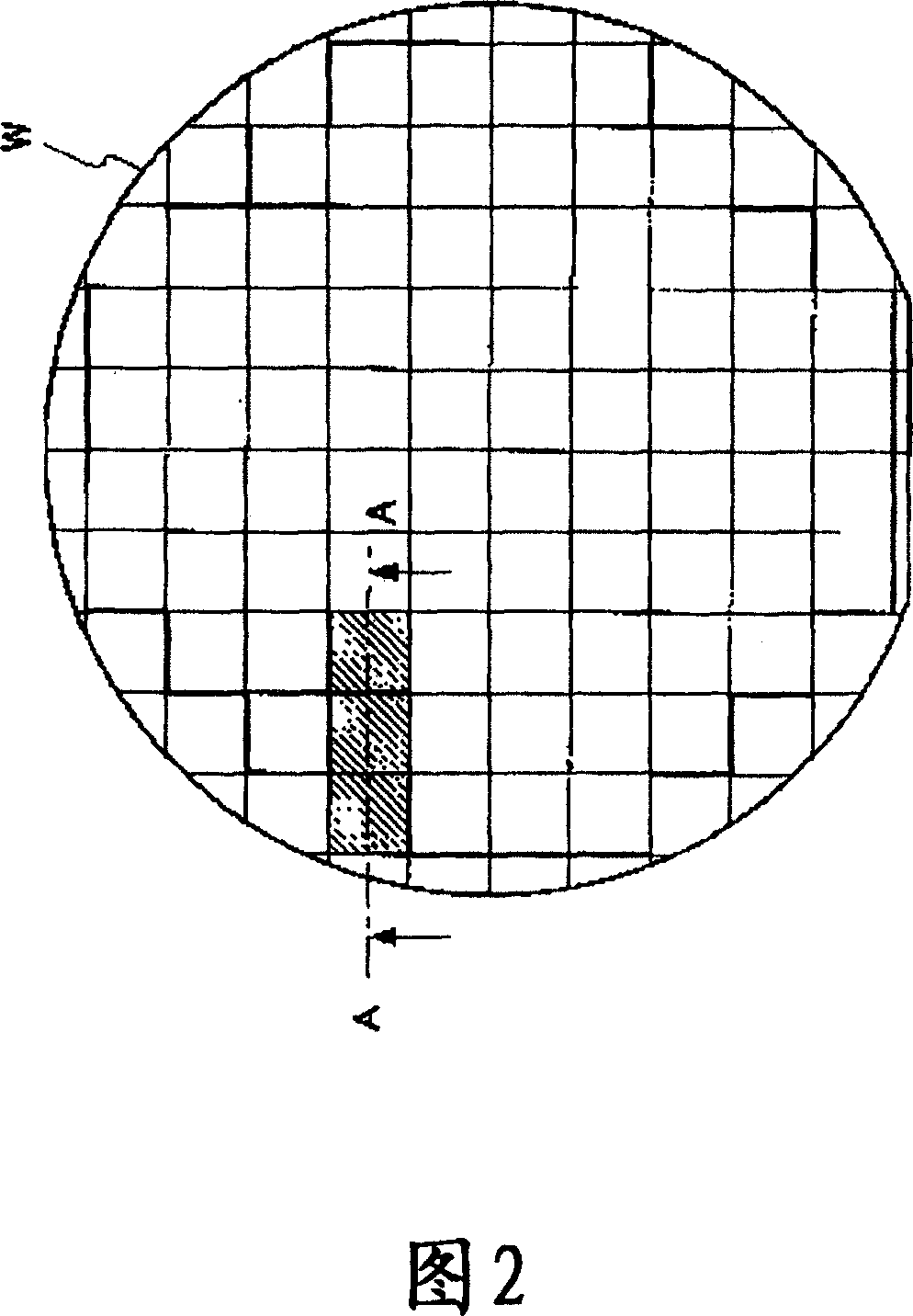

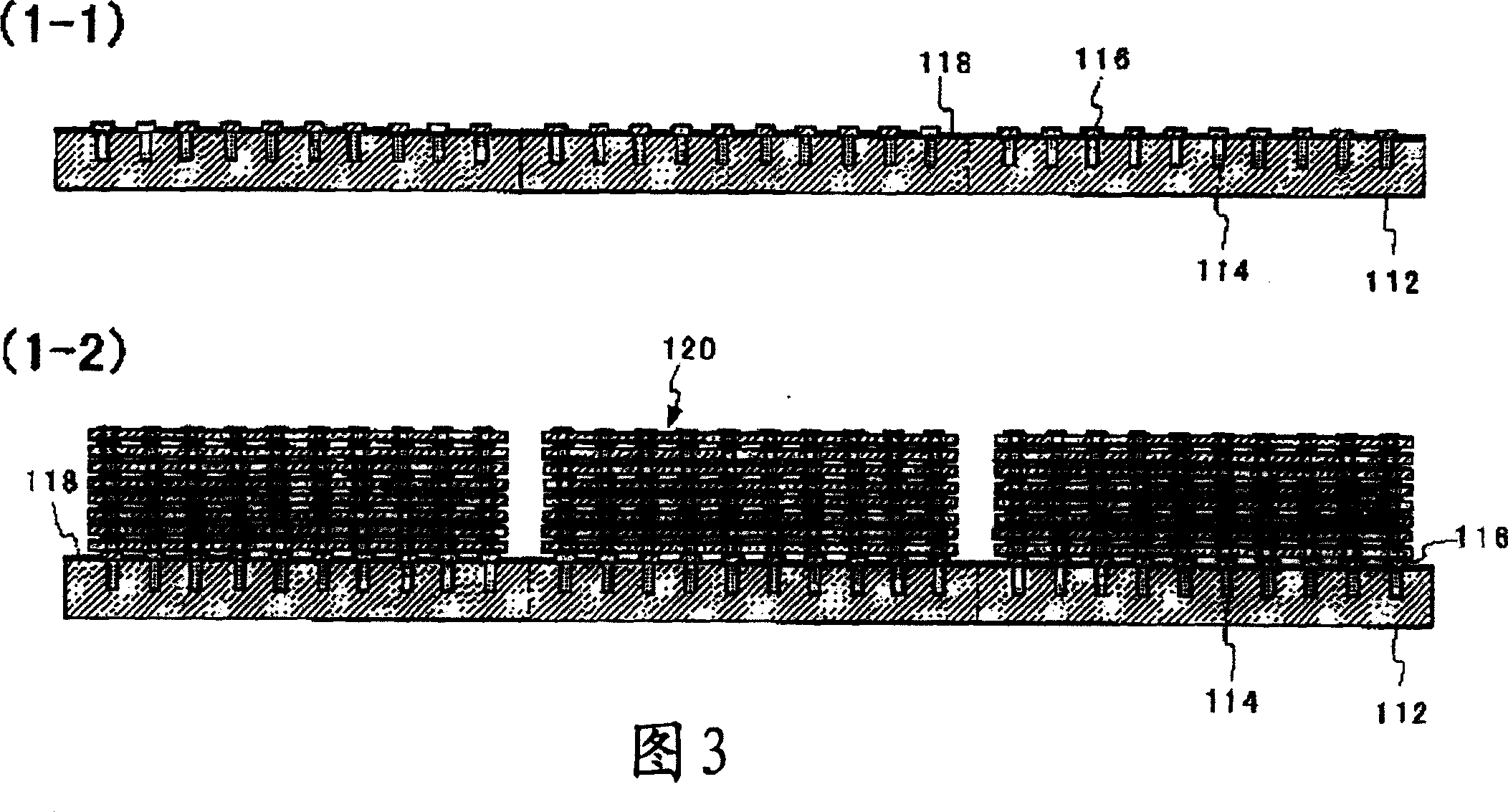

[0028] Hereinafter, the best mode for carrying out the present invention will be described in detail using examples. FIG. 1 is a schematic cross-sectional view showing the structure of a semiconductor chip (A) and its laminate (B) applicable to a semiconductor package according to the present invention. 2 is a schematic plan view showing a silicon wafer for an interposer applicable to the semiconductor package of the present invention. The semiconductor chip 100 has a structure in which bumps 106 are formed on both surfaces of the front and rear surfaces of the semiconductor substrate 102 on which the penetrating electrodes 104 are provided. In addition, a structure in which the bump 106 is formed only on one side of the semiconductor substrate 102 may also be used. The thickness of the semiconductor substrate 102 is desirably 20 to 100 μm from the depth of the through-electrodes. For convenience of description, it is assumed that the structure in which the semiconductor chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com